#### AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING CAIRO, EGYPT

**Electronics and Communications Department**

# CAD for 3D Integration - Static Timing Analysis (3D-STA)

A Thesis

Submitted in Partial Fulfillment for the Requirements of the Degree of

Master of Science in Electrical Engineering

Electronics and Communications Department

#### Submitted by

Mohamed Nasr Ahmed El Bahey

BSc. of Electrical Engineering Electronics and Communications Department Cairo University, 2008.

#### Supervised by

Prof. Hani Fekri Ragai

Dr. DiaaEldin Sayed Mahmoud Khalil

Cairo 2016

#### AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING CAIRO, EGYPT

Electronics and Communications Department

### **Examiners Committee**

**Thesis**: CAD for 3D Integration - Static Timing Analysis (3D-STA)

Name: Mohamed Nasr Ahmed El Bahey

Date:

**<u>Degree</u>**: Master of Science in Electrical Engineering

| Name, Title, and Affiliation                                                                                     | <u>Signature</u> |

|------------------------------------------------------------------------------------------------------------------|------------------|

| Prof. ElSayed Mostafa Saad Electronics and Communications Eng. Dept Faculty of Engineering, Helwan University    |                  |

| Prof. Mohamed Amin Dessouky Electronics and Communications Eng. Dept Faculty of Engineering, AinShams University |                  |

| Prof. Hani Fekri Ragai Electronics and Communications Eng. Dept Faculty of Engineering, AinShams University      |                  |

#### **STATEMENT**

This thesis is submitted to Ain Shams University in partial fulfillment for the degree of Master of Science in Electrical Engineering.

The work included in this thesis was carried out by the author in the Department of Electronics and Communications Engineering, Ain Shams University, Cairo, Egypt.

No part of this thesis has been submitted for a degree or a qualification at any other university or institute.

Name: Mohamed Nasr Ahmed EL Bahey

Signature:

Date:

#### Curriculum Vitae

Name of the Researcher: Mohamed Nasr Ahmed El Bahey

**Date of Birth**: 5<sup>th</sup> of September, 1985.

**Place of Birth:** Cairo, Egypt.

University Degree: BSc. in Electrical Engineering

Electronics and Communications Department,

Cairo University.

Year of Graduation: June, 2008.

#### AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING CAIRO, EGYPT

**Electronics and Communication Department**

# CAD for 3D Integration - Static Timing Analysis (3D-STA)

#### Submitted by

Mohamed Nasr Ahmed El Bahey

#### Supervised by

Prof. Hani Fekri Ragai and Dr. DiaaEldin Khalil

#### **English Summary**

This work explores enabling existing flow and tools to handle full 3D designs without introducing drastic changes or excessive computations.

It focuses on full 3D design Static Timing Analysis (STA) with routing parasitic for its critical importance in the digital design flow. It proposes and implements an STA framework "3D-STA" that efficiently handles full 3D extracted digital designs, as well as, regular planar ones. It presents details on the Through Silicon Via (TSV) extraction model, connectivity representation and delay calculations.

This thesis is divided into six chapters including lists of contents and figures as well as list of references.

**Chapter 1:** Includes introduction and thesis motivation. This chapter ends with thesis outline.

**Chapter 2**: Contains brief on 3D integration, brief introduction to Through Silicon Via structure and fabrication techniques.

**Chapter 3:** Discusses in details the enabling of CAD tools for 3D integrated circuit design and introduces the challenges for planar CAD tools in handling 3D ICs.

**Chapter 4:** Discusses in details Static Timing Analysis technique and algorithm for integrated circuits.

**Chapter 5**: Proposes a simplified electrical lumped model for TSV and how to be introduced in signal path delay.

**Chapter 6**: Introduces the developed 3D-STA framework and presents the expremental results of processing ISCAS'85 benchmarks.

**Chapter 7**: Discusses the conclusions and suggestions for Future Work.

### Acknowledgment

#### ALL THE PRAISES AND THANKS BE TO ALLAH

Praise be to Almighty ALLAH for his endless blessings.

It has been an extraordinary journey, yet a challenging one.

Completing a M.Sc. is, no doubt, a monumental task that needs effort, discipline, courage and among other things, a good deal of help from external sources.

Thus, as I am nearly reaching the end of the journey, I would like to express my gratitude to individuals who have played prominent roles in completing this thesis.

As a beginning, I would like to thank **my supervisors**,

**Prof.** Hani Fekry Ragai

**Dr**. DiaaEldin Khalil

Special thanks to **Prof. Hany Fekry Ragai** for his guidance, patience and encouragement through the years of my M.Sc.

Special thanks to **Dr. DiaaEldin Khalil**, my teacher and mentor for his guidance, extra ordinary efforts and encouragement, his support and smart ideas was the only guid through the years of my M.Sc.

Great love and thanking goes to my dear and great **parents**, who, without their support and encouragement I wouldn't have accomplished this thesis and wouldn't have achieved anything in my life without their prayings.

Special thanks go to my friend **Mahmoud Salah**, who helped me in solving many problems I faced during my research & who encouraged me through the journey.

Finally, special thanks go to my great, helpful and amazing sisters **Salwa**, **Nahed** and **Sawsan** for their support during this interesting knowledge journey.

## **Table of Contents**

| Ta | ble of C | Contents                                    | II |

|----|----------|---------------------------------------------|----|

| Ta | ble of F | ïguresI                                     | V  |

| Та | ble of T | ables                                       | V  |

| Li | st of Ab | breviations                                 | VΙ |

| ΑI | BSTRA    | CT                                          | .1 |

| 1. | Cha      | pter 1 Introduction                         | .2 |

|    | 1.1      | Moore's Law and Interconnect Bottleneck     | 2  |

|    | 1.2      | Motivation and Background of 3D ICs         | 3  |

|    | 1.3      | Benefits of 3D Integration                  | 4  |

|    | 1.4      | Challenges in 3D Integration                | 5  |

|    | 1.5      | Problem Statement                           | 6  |

|    | 1.6      | Thesis Organization                         | 6  |

| 2. | Cha      | pter 2 3D Integration Background            | .7 |

|    | 2.1      | Introduction                                | 7  |

|    | 2.2      | TSV Structure                               | 8  |

|    | 2.3      | TSV Fabrication and Types of Via Creation   | 10 |

| 3. | Cha      | pter 3 Enabling CAD for 3D Integration      | 2  |

|    | 3.1      | Limitations of Current 2D CAD Tools         | 12 |

|    | 3.2      | Efforts to create 3D CAD tools              | 13 |

|    | 3.3      | Parasitic Extraction                        | 14 |

|    | 3.4      | Parasitic Extraction Evolution.             | 15 |

|    | 3.5      | Floor-planning and Physical Design Overview | 15 |

|    | 3.6      | Placement and Routing Overview              | 16 |

| 4. | Cha      | pter 4 Static Timing Analysis1              | 7  |

|    | 4.1      | Introduction                                | 17 |

|    | 4.2      | Static Timing Analysis Overview             | 17 |

|    | 4.3      | Benefits of Static Timing Analysis          | 17 |

|    | 4.4      | Timing Verification                         | 17 |

|    | 4.5      | Output Cases of Static Timing Analysis      | 18 |

|     | 4.6     | Static timing Analysis Procedures                                  | 19 |

|-----|---------|--------------------------------------------------------------------|----|

|     | 4.6     | 1 Timing Graph Construction                                        | 20 |

|     | 4.7     | Static Timing Analysis Algorithms                                  | 21 |

|     | 4.7     | 1 Arrival-Time-Propagation                                         | 22 |

|     | 4.7     | 2 Required-Time-Propagation                                        | 23 |

| 5.  | Cha     | apter 5 Simplified Electrical Lumped Model for Through Silicon Via | 26 |

|     | 5.1     | Introduction                                                       | 26 |

|     | 5.2     | Proposed TSV Circuit Model                                         | 26 |

|     | 5.3     | Proposed Idea for 3D CAD tools                                     | 28 |

|     | 5.4     | Handling TSV in parasitic extraction                               | 29 |

|     | 5.5     | TSV Insertion into SPEF/DSPF File                                  | 30 |

| 6.  | Cha     | pter 6 3D-STA Framework                                            | 32 |

|     | 6.1     | Introduction                                                       | 32 |

|     | 6.2     | 3D-STA Framework capabilities                                      | 32 |

|     | 6.3     | 3D-STA Framework Flow                                              | 33 |

|     | 6.4     | Horizontal Wires and TSVs Delay Calculation                        | 35 |

|     | 6.5     | 3D-STA Gate Delay Calculation Analysis                             | 36 |

|     | 6.6     | Graphical User Interface (GUI)                                     | 36 |

|     | 6.7     | Framework Output                                                   | 38 |

|     | 6.8     | Simulation Results                                                 | 40 |

|     | 6.8     | 1 3D-STA Run Time Analysis:                                        | 42 |

|     | 6.8     | 2 3D-STA Memory Usage Analysis:                                    | 43 |

|     | 6.8     | 3 3D-STA CPU Usage Percentage Analysis:                            | 44 |

|     | 6.8     | 4 3D-STA Comparison with other tools                               | 45 |

| 7.  | Cha     | apter 7 Conclusions and Suggestions for Future Work                | 46 |

| 8.  | Bib     | liography                                                          | 48 |

| Δ11 | ıthor's | Publications                                                       | 54 |

# Table of Figures

| FIGURE 1-1 DELAY FOR METAL 1 AND GLOBAL WIRING VERSUS FEATURE SIZE | 3  |

|--------------------------------------------------------------------|----|

| FIGURE 2-1 CONCEPTUAL DIAGRAM OF A 3D STACKED IC                   | 7  |

| FIGURE 2-2 3D IC STACKED DIE                                       | 8  |

| FIGURE 2-3 TSV STRUCTURE                                           | 9  |

| FIGURE 2-4 CROSS-SECTION OF TSV [20]                               | 9  |

| FIGURE 2-5 3D IC FABRICATION PROCESS                               | 11 |

| FIGURE 2-6 3D IC FABRICATION DIAGRAM                               | 11 |

| FIGURE 3-1 DIGITAL DESIGN FLOW                                     | 14 |

| FIGURE 3-2 EXAMPLE ROUTE FOR A NET IN A THREE-TIER 3D DESIGN       | 16 |

| FIGURE 4-1 SETUP AND HOLD TIME CONSTRAINTS ON PATH DELAYS          | 18 |

| FIGURE 4-2 OUTPUT CASES OF STATIC TIMING ANALYSIS DIAGRAM          | 19 |

| FIGURE 4-3 CIRCUIT TO TIMING GRAPH DIAGRAM                         | 21 |

| FIGURE 4-4 SLACK CALCULATION GRAPH                                 | 24 |

| FIGURE 4-5 STATIC TIMING ANALYSIS ALGORITHM FLOWCHART              | 25 |

| FIGURE 5-1 SIMPLIFIED ELECTRICAL TSV MODEL FOR STA                 | 26 |

| FIGURE 5-2 MODEL OF TIER-TO-TIER VERTICAL CHANNEL                  | 27 |

| FIGURE 5-3 A-DRIVER TIER DSPF FILE, B-DESTINATION TIER DSPF FILE   | 30 |

| FIGURE 5-4 TSV INSERTION TOOL BY NUMBERS                           | 31 |

| FIGURE 5-5 TSV INSERTION TOOL BY PERCENTAGE                        | 31 |

| FIGURE 6-1 3D-STA FRAMEWORK FLOWCHART                              | 34 |

| FIGURE 6-2 EXAMPLE TREE OF TSV CONNECTING TWO WIRES                | 35 |

| FIGURE 6-3 GUI FOR 3D-STA FRAMEWORK                                | 37 |

| FIGURE 6-4 DESIGN CONNECTIVITY GRAPH                               | 39 |

| FIGURE 6-5 DESIGN CONNECTIVITY DELAYS GRAPH                        | 39 |

| FIGURE 6-6 DESIGN STATIC TIMING ANALYSIS GRAPH                     | 40 |

| FIGURE 6-7 RUN TIME (%) COMPARED TO 0% TSV INSERTION               | 42 |

| FIGURE 6-8 GRAPHICAL REPRESENTATION FOR RUN TIME ANALYSIS          | 43 |

| FIGURE 6-9 GRAPHICAL REPRESENTATION FOR MEMORY USAGE ANALYSIS      | 44 |

| FIGURE 6-10 GRADHICAL REPRESENTATION FOR MAY CPULLS AGE            | 45 |

## Table of Tables

| Table 1 TSV process flows                                                      | 10 |

|--------------------------------------------------------------------------------|----|

| Table 2 ISCAS85 benchmark circuits                                             | 40 |

| Table 3 Timing analysis excluding interconnect propagation delay               | 41 |

| Table 4 Timing analysis including interconnect propagation delay               | 41 |

| Table 5 Run time analysis for ISCAS 85 for different TSV insertion percentages | 42 |

| Table 6 Memory usage analysis for ISCAS 85                                     | 43 |

| Table 7 Max CPU Usage analysis for ISCAS 85                                    | 44 |

| Table 8 Run time, maximum CPU usage, and maximum memory usage                  | 45 |

### List of Abbreviations

TSV Through Silicon Via

STA Static Timing Analysis

ITRS International Technology Roadmap for Semiconductors

CAD Computer-aided design

SPEF Standard Parasitic Exchange Format

DSPF Detailed Standard Parasitic Format

GUI Graphical user interface

Ts Setup Time

Th Hold Time

Tp Period Time

dp Path Delay

Arr<sub>min</sub> Minimum Arrival Time

Arr<sub>max</sub> Maximum Arrival Time

Req<sub>min</sub> Minimum Required arrival Time

Req<sub>max</sub> Maximum Required Arrival Time

#### **ABSTRACT**

3D integration presents a paradigm shift that will enable larger cell integration, through the stacking of multiple layers (tiers) using bonding and Through Silicon Vias (TSVs). 3D integration introduces several benefits in delay areas and foot print.

The use of three dimensional chip fabrication technologies has emerged as a solution for the difficulties related to the continuous scaling of bulk silicon devices. Although the technology already exists, it is undervalued and underutilized largely due to the design and verification challenges that a complex 3D design presents.

CAD tools that are capable of dealing with 3D integrated circuits are still under development. In this work a proposed Static Timing Analysis (STA) tool is presented with a new technique to handle effectively 3D integration with minimum modifications. In addition, a proposed simplified lumped model for TSV is also presented and has been inserted into the framework delay calculations.

The proposed 3DIC timing verification tool serves as an efficient mean to perform all setup and hold timing checks, in which the multi-die design will not be transformed to appear as a traditional 2D design in verification purposes.

### **Chapter 1 Introduction**

#### 1.1 Moore's Law and Interconnect Bottleneck

Any digital system is composed of three main components: memory, data path and control logic. The performance in such systems primarily depends on how well these components can perform the required tasks while communicating with each other.

At a lower level the two key factors that determine the overall performance of a digital system are device delay and interconnect delay. One approach to achieve higher performance is by technology scaling.

By scaling, the channel length of the device is reduced. In other words, the charge carriers have to travel smaller distances in order to reach the drain terminal from the source terminal. Scaling reduces the amount of time taken to move charge carriers from source to drain, thus resulting in faster circuits. The voltage required to drive the charge carriers after creating the channel is also reduced. This is significant as it reduces the amount of power consumed by the system.

**Reduced device and interconnect delay** help to add more components on a single integrated circuit in compliance with Moore's law [1]. According to Moore's law, the number of transistors that can be added to an integrated circuit doubles every two years. Thus technology scaling has been the driving force behind the semiconductor industry to stay in course with Moore's law.

As a result, interconnect which is relatively slow compared to a device in terms of delay, determines the overall performance of an integrated circuit.

Furthermore, the increased functionality due to scaling has led to the scenario where the overall power is dominated by interconnects. Hence, there is a need for new methodology to tackle this problem of interconnect bottleneck.

#### 1.2 Motivation and Background of 3D ICs

As technology scales, the International Technology Roadmap for Semi-conductors (ITRS) projecting on-chip communication, will require new design approaches to achieve system-level performance targets.

Aggressive scaling of process technologies has enabled feature sizes to shrink continuously. While the performance of gates has been improving, interconnects have become a major performance bottleneck [2-4], because global interconnects do not scale accordingly with technologies.

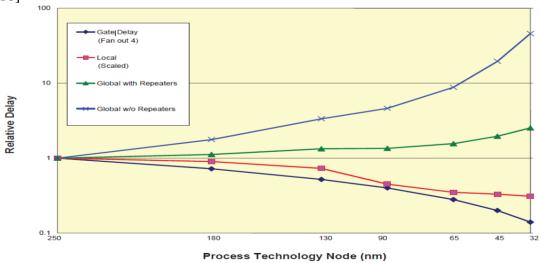

Consequently, interconnect has emerged as the dominant source of circuit delay and power consumption. Figure 1-1 shows the delay of metal and global wiring in future generations. It indicates that with technology scaling, gate delay and local interconnect delay decrease, but global delay increases dramatically. Repeaters can be incorporated to mitigate the delay in global wiring, but this will consume power and chip area.

Therefore, the reduction of interconnect delays and power consumption are of paramount importance for deep-submicron designs. Therefore, numerous research efforts are currently devoted to seeking solutions that can overcome the limitation of wiring requirements for present and future chip designs.

While there have been significant interconnect technology improvements over the last few years, such as the use of copper and low-K dielectric, the industry is striving for additional improvements. Three-dimensional (3D) ICs have recently emerged as a promising means to mitigate these interconnect-related problems [5-10]

Figure 1-1 Delay for Metal 1 and Global Wiring versus Feature Size (Source: International Technology Roadmap for Semiconductors)