# MODELING OF THE DYNAMIC PERFORMANCE OF MOSFETS USING SPICE

Ву

#### SHEREEF BASSIOUNI MOHAMMAD SHEHATA

B.Sc. in Electrical Engineering

**THESIS**

Submitted in Partial Fulfillment For The

Requirements for the Degree of

Master of Science

5, B ELECTRICAL ENGINEERING

SUPERVISED BY

Prof. Dr. M. MARZOUK IBRAHIM

Dr. HISHAM S.R. HADDARA

w1206

ELECTRONICS AND COMPUTER ENGINEERING DEPARTMENT

FACULTY OF ENGINEERING

AIN SHAMS UNIVERSITY

1991

### **EXAMINERS COMMITTEE**

# Signature NAME, Title & Affiliation M. Marzouk Ibrahim Prof. Dr. M. Marzouk Ibrahim 1-Head of Electronics and Computer Eng. Dept., Faculty of Eng., Ain-Shams University Serag Habit 2- Prof. Dr. Serag El-din Habib Electrical Eng. Dept., Faculty of Eng., Cairo University Prof. Dr. Hani F. Ragaie 3-Electronics and Computer Eng. Dept., Faculty Of Eng., Ain-Shams University Date .30/// 1991

#### ACKNOWLEDGMENT

I would like to express my deep thanks to **Prof. M. Marzouk Ibrahim**, Head of The Electronics and Computer Engineering Department, Ain-Shams University ,for best supervision , useful discussions and critical reading of the manuscript. His support and help are without measure.

I feel greatly indebted to Prof. Dr. H. F. Ragaie for his valuable suggestions and discussions and for his endless patience.

Special thanks to **Dr. Hisham Haddara** who inspired this work with valuable ideas and discussions. His support and guidance throughout this work are most appreciated.

Last but not least, thanks to Eng. Walid Khairy , Eng. Haytham Al-Guindy and Eng. Mohamed Abd Al Moneim., for their friendly help.

## STATEMENT

This dissertation is submitted to Ain Shams University for the degree of Master Of Science in Electrical Engineering. The work included in this thesis was carried out by the author in the Department of Electronics and Computer Engineering, Ain Shams University, from November 1989 to October 1991. No part of this thesis has been submitted for a degree or a qualification at any other University or Institution.

Date :

Signature : There? There?

Name : Saeres Caparound

## MODELING OF THE DYNAMIC PERFORMANCE OF MOSFETS USING SPICE

### **ABSTRACT**

This thesis deals with the modeling of the dynamic performance of MOS devices which constitute the main building block of modern integrated circuits. A distributed equivalent circuit and a novel approach for modeling such devices using the circuit simulator SPICE are proposed in this work. Simulation of uniform channel devices as well as devices with random charge distributions and local damage of the gate oxide has been performed.

Chapter one is an introduction to the theoretical basis of the dynamic performance of MOSFETs. Also, a brief summary of the existing small signal models of MOS transistors is presented and the device parameters related to the dynamic performance are introduced. Finally, a brief description of the circuit simulator SPICE is given.

Chapter two is devoted to the simulation of the dynamic behaviour of devices with uniform charge distributions inside the gate oxide. The channel time constant is simulated for several values of the technological parameters and its dependence on the interface trap density is studied.

Chapter three deals with locally damaged devices as well as those with random interface charge distributions. The simulation approach used to deal with these two problems is presented and the results obtained from the analysis are discussed.

Experimental measurements have been carried out on several devices and their results are presented in chapter four. Comparison to the results of SPICE simulations shows that a very good agreement exists between the experimental and the simulation results indicating that the proposed approach is quite accurate.

Finally, concrete conclusions as well as the proposed directions of future study are indicated.

## TABLE OF CONTENTS

## CHAPTER 1

## INTRODUCTION

| 1-1 | SMALL-SIGNAL MODELS FOR THE MOS CAPACITOR    | 1  |

|-----|----------------------------------------------|----|

| 1-2 | SMALL-SIGNAL MODELS FOR THE MOS TRANSISTOR   | 8  |

| 1-3 | THE SPICE PROGRAM                            | 13 |

|     | 1-3-1 Introduction                           | 13 |

|     | 1-3-2 A.C. Small-Signal Analysis             | 13 |

|     | 1-3-3 Iput File                              | 15 |

|     | 1-3-4 The MOSFET Small-Signal Model In SPICE | 17 |

| 1-4 | THE BASIC PARAMETERS USED FOR SIMULATION     | 18 |

## CHAPTER 2

# SIMULATION OF THE DYNAMIC PERFORMANCE OF THE UNIFORM MOS TRANSISTOR

| 2-1 | SMALL- | SIGNAL EQUIVALENT CIRCUIT OF THE UNIFORM | TRANSISTOR |

|-----|--------|------------------------------------------|------------|

| 2-2 | SPICE  | SIMULATION TECHNIQUE                     | 28         |

|     | 2-2-1  | Operating Point Analysis                 | 28         |

|     | 2-2-2  | A.C. Analysis                            | 29         |

|     | 2-2-3  | The Use Of Subcircuits                   | 30         |

|     | 2-2-4  | The Use Of Idle Voltage Sources          | 30         |

|     | 2-2-5  | Probing Of MOSFET Transfer Admittance    | 31         |

| 2-3 | SIMULA | TION RESULTS                             | 32         |

|     | 2-3-1  | Effect Of Frequency On Admittance        | 32         |

|     | 2-3-2  | Effect Of Bias On Admittance             | 63         |

|     | 2-2-3  | Channel Time Constant                    | 71         |

| 2-4 | TRANSC | ONDUCTANCE SIMULATION                    | 77         |

|     | 2-4-1  | Simulation Technique                     | 79         |

|     | 2-4-2  | Simulation Results                       | 83         |

# CHAPTER 3

| SIMULATIONN OF THE DYNAMIC PERFORMANCE OF MOSFET   | Ts 89 |  |  |

|----------------------------------------------------|-------|--|--|

| WITH INTERFACIAL NONUNIFORMITIES                   |       |  |  |

|                                                    |       |  |  |

| 3-1 SIMULATION OF LOCALLY DAMAGED CHANNEL          | 90    |  |  |

| 3-1-1 The Current Understanding Of                 | 90    |  |  |

| The Hot Carrier Problem                            |       |  |  |

| 3-1-2 Simulation Technique                         | 94    |  |  |

| 3-1-3 Effect Of Frequency On Admittance            | 97    |  |  |

| 3-1-4 Effect Of Frequency On Bias                  | 110   |  |  |

| 3-2 TRANSCONDUCTANCE SIMULATION                    | 134   |  |  |

| 3-3 SIMULATION OF MOSFET WITH                      | 136   |  |  |

| STATISTICAL CHARGE FLUCTUATIONS                    | 100   |  |  |

| 3-3-1 Simulation Technique                         | 144   |  |  |

| 3-3-1-1 The Monte-Carlo (MC) Method                | 144   |  |  |

| 3-3-1-2 Monte-Carlo Analysis In Circuit Simulators | 145   |  |  |

| 3-3-1-3 Simulation Of Interface Nonuniformities    | 145   |  |  |

| Using The MC Method                                | - 10  |  |  |

| 3-3-2 Simulation Results                           | 146   |  |  |

|                                                    | 140   |  |  |

|                                                    |       |  |  |

| CHAPTER 4                                          |       |  |  |

| MEASUREMENTS AND CONDIDERS MALE                    |       |  |  |

| MEASUREMENTS AND COMPARISON WITH SIMUALTION        | 154   |  |  |

| 4-1 EXPERIMENTAL DETAILS                           |       |  |  |

| 4-1-1 Amplitude Of The Small Signal                | 154   |  |  |

| 4-1-2 Noise Reduction And Stability                | 155   |  |  |

| 4-1-3 Measurement setups                           | 158   |  |  |

| 4-1-4 Measurement Results                          | 158   |  |  |

| 4-1-5 Artificial Aging Of Devices                  | 160   |  |  |

| 4-1-6 Measurements After Stress                    | 167   |  |  |

| 4-2 COMPARISON BETWEEN MEASUREMENT AND SIMULATION  | 175   |  |  |

| DETREER REASUREMENT AND SIMULATION                 | 189   |  |  |

| Conclusion                                         |       |  |  |

| LIST OF REFERENCES                                 |       |  |  |

| LINE TOTAL                                         |       |  |  |

#### CHAPTER 1

#### INTRODUCTION

In this chapter a brief review of the existing small signal models for MOS devices is presented. The basic parameters representing the dynamic behavior of the MOS transistor is presented. Also a brief description of the SPICE program is given along with the A.C. small signal MOSFET model available in SPICE.

#### 1-1 SMALL-SIGNAL MODELS FOR THE MOS CAPACITOR

The small signal equivalent circuit model of the MOS capacitor has been treated in literature in several ways, the transmission-line modeling of MOS capacitors is one of these methods. One of the earliest models for the MOS capacitor was introduced by Lehovec and Slobodskoy [1], their methodology to arrive at an equivalent circuit was to follow step by step the flow of A.C. charges, electrons and holes, from the bulk of the semiconductor to the interface between the semiconductor and the oxide. Each step can be associated with a resistor. Accumulation of A.C. charges can be associated with capacitors, finally, they have reached a lumped circuit model obtained from physical considerations and charge analysis [1].

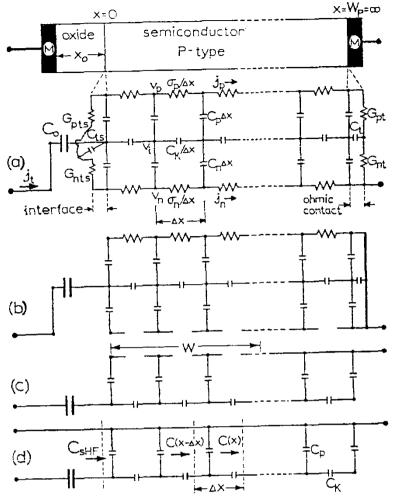

C.T.Sah et al. [2] have used a small signal expansion of the transport equations, these transport equations can be synthesized to give the complete equivalent circuit of the semiconductor region for one dimensional geometry as shown in Fig.(1.1) where  $C_o$  is the oxide capacitance,  $G_{\rm pst}$ ,  $G_{\rm nst}$  and  $C_{\rm ts}$  represent the carrier capture conductance and storage

Fig. (1.1). The upper part shows the MOS structure where M is the metal contact. (a) The complete equivalent circuit including surface states at x = 0 and the ohmic contact at x = ∞, but excludes recombination in the bulk.

(b) The complete high frequency equivalent circuit with an ideal ohmic contact. (c) The high frequency equivalent circuit for an inverted surface.

(d) The high frequency equivalent circuit for a non-inverted surface which is also valid for an inverted surface.

Inversion layer flows through an MOS capacitor in the presence of an external inversion layer (After Nicollian E.H. and Goetzberger A.

capacitance at the interface states, and  $G_{pt}$ ,  $G_{nt}$  and  $C_t$  those at the ohmic contact. Here  $C_p = q^2 p/kT$ ,  $C_n = q^2 n/kT$ ,  $C_k = \epsilon_{so}$ ,  $\sigma_p = q\mu_p p$  and  $\sigma_n = q\mu_n n$ . p and n are the static hole and electron concentrations,  $C_k$  is the permittivity of the semiconductor,  $\mu_p$  and  $\mu_n$  are the carrier mobilities in the bulk.

In the high frequency range, the electron (minority carrier) conductance  $\sigma_n$  is removed since minorities can not be supplied at a sufficiently rapid rate to follow the signal frequency. Thus the equivalent circuit simplifies to that in Fig.(1.1.b). The transmission-line can be further simplified for non-intrinsic surfaces as follows:-for an inverted surface, there is a hole (majority) depletion layer, 0 < x < W, where  $C_p = \sigma_p = p = 0$ . In the bulk, x > W,  $\sigma_p$  can be shorted if the signal frequency is much less than the dielectric relaxation time of majority carriers,  $(\sigma_p/C_k)$ . These considerations are shown in Fig.(1.1.c). For a non-inverted surface,  $p \gg n_i$ , so that  $\omega \ll \sigma_p/C_k$  also in the surface layer 0 < x < W, giving Fig.(1.1.d). However, since  $C_p = 0$  for 0 < x < W in the inverted surface case, Fig.(1.1.d) actually represents both the inverted and non-inverted surface conditions.

These considerations show that  $\sigma_p$  contributes a large semiconductor conductance only near the intrinsic surface condition where a conductance peak is often observed experimentally. Y.C.Sun and C.T.San [3] more recently proposed a one dimensional small signal equivalent circuit of the MOS capacitor very close to that in Fig.(1.1), but including bulk traps, and also a two dimensional small signal equivalent circuit including interface edge effects [3].

These equivalent circuits were considered to be very complex [4] and it is interesting to note that they can be simulated using SPICE, using

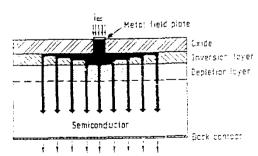

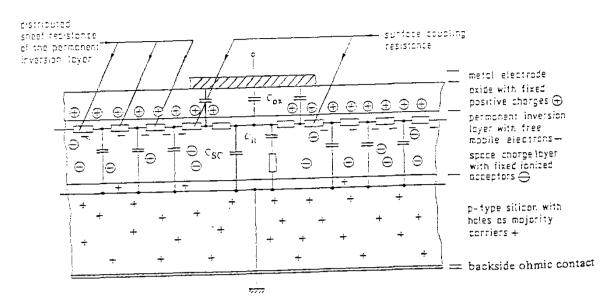

- Equivalent circuit of a MOS structure in the presence of a permanent inversion layer.

- Directly below the metal gate, we have a normal MOS capacitor, schematically represented here by  $C_{\rm DX}$ ,  $C_{\rm SC}$  and  $C_{\rm it}$

- Beyond the metal gate, the permanent inversion layer forms a transmission line with a low-pass filter characteristic.

- The intrinsic MOS capacitor and the permanent inversion layer (or channel) are connected by the surface coupling resistor. Its resistance is bias-dependent.

Fig. (1.3)

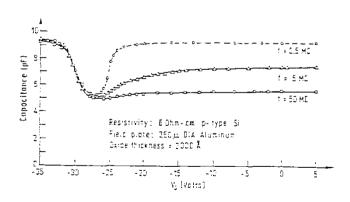

Behavior of an MOS capacitor in the presence of a permanent inversion layer,  $C_{ij}$  is plotted versus  $V_G$  as a function of frequency. The usual lift behavior is only found for frequencies above the cut-off frequency of the external channel [70 MHz here]. (After Nicollian, E.H. and Goetzberger A.

4

approximately the same technique as the one described in chapter-2 for the MOS transistor.

On the other hand, S.R.Hofstein and G.Warfield [5] have used a transmission-line model to analyze the lateral transfer of inversion charges which were supplied by the inverted regions cutside the gate area. E.H.Nicollian and A.Goetzberger [6] have also used a transmission-line model, for the same purpose; their solution for the circular gate structure was in the form of Bessel functions.

In these two papers [5,6], they suggested a model like that outlined in Fig. (1.3).

In this model three components can be distinguished: -

- The intrinsic MOS capacitor: which can be represented by the equivalent circuit commonly used , i.e. made up of oxide capacitance. of the space charge capacitance and of the capacitance C, due to interface states.

- The permanent inversion layer: Its electrons are free to move. The permanent inversion layer reacts in a double way to electric fields: in a direction parallel to the interface it behaves like a sheet resistance and in direction perpendicular to the interface, the inversion layer is capacitively coupled to the majority carriers of the semiconductor. The permanent inversion layer is therefore represented by a distributed resistance-capacitance network. It can be viewed as a transmission-line with low-pass filter characteristics.

3- The surface coupling resistance: it connects the MOS capacitor to the external channel and its value is bias dependent.

Fig. (1.4) shows the C(V) curves of this structure, the accumulation and depletion branches of the C(V) curves behave quite normally, because in these bias regimes the external inversion channel is disconnected from the MOS capacitor and exerts no influence. In inversion however, the channel is closely connected to the MOS capacitor and the rise of the high frequency capacitance is a direct consequence of this coupling. The input admittance of the channel shunts the space charge capacitance of the intrinsic MOS capacitor [4]. In what proportion the total A.C. current divides itself between the space charge (depletion) capacitance and the external channel depends on the frequency of the test signal. The channel current first spreads laterally before being led away through the capacitive leakage. The size of the area through which most of the channel current flows, is a measure of the effective shunt capacitance. It increases when the frequency decreases as the channel behaves like a low pass filter network.

Fig. (1.2) shows a representation of how this AC current flows. It is interesting that the C(V) curves in Fig. (1.3) is similar to that of the MOS transistor when its source, drain and substrate are tied together and grounded.

The above transmission-line models for the MOS capacitor with a surrounding extrinsic inversion layer, initiated the thought of similar transmission-line models to be applied for the MOS transistor, (which have a rectangular structure) to study its behavior. These models are presented in the next section.