#### AIN SHAMS UNIVERSITY FACULTY OF ENGINEERING CAIRO-EGYPT

# FPGA Implementation of Digital Image Enhancement Techniques

Thesis submitted in partial fulfillment of the requirement for the degree of Master of Science

By

#### Eng. Tarek Mohamed I. Al Bittibssi

B.Sc. Electric Engineering Military Technical Collage, 2000

Supervisors:

## Prof. Adel Ezzat Mohamed El Hennawy

Faculty of Engineering- Ain Sahms University

#### Assistant Prof. Gouda Ismail Mohamed

Military Technical Collage

#### Assistant Prof. Yahya Zakaria Mohasseb

Military Technical Collage

Cairo 2013

### **Examiners Committee**

The undersigned certify that they have read and recommend to the Faculty of Engineering - Ain shams University for acceptance a thesis entitled "FPGA implementation of digital image enhancement techniques" submitted by Tarek Mohamed Al Bittibssi, in partial fulfillment of requirement for the degree of Master in Science in Electric Engineering.

Signature

Prof. Adel Ezzat El hennawy

Faculty of Engineer - Ain Shams University

Prof. El-Sayed Mostafa Saad

Faculty of Engineer - Helwan University

**Prof. Abdel Haliem Zakery**

Faculty of Engineer - Ain Shams University

**Assistant Prof. Gouda Ismail Mohamed**

Military Technical Collage

## Statement

This thesis is submitted in the partial fulfillment of master degree in Electrical Engineering to Ain Shams University.

The author carried out the work included in this thesis, and no part of this thesis has been submitted for a degree or qualification at any other university.

Signature

Tarek Mohamed Al Bittibssi

# Acknowledgment

First of all, I thank GOD who guided and helped me to finish this work in the proper shape.

I would like to express my sincere gratitude and love to my family for continuous support and encouragement throughout my life. Also my wife deserves my wholehearted thanks as well.

I would like to express my deep appreciation to Prof. Adel Ezzat El Henawy Professor in electrical engineering, faculty of engineering Ain Shams University, for his guidance and valuable suggestion, I'm also extremely grateful to Dr. Gouda Ismail Mohamed and Dr. Yehya mohasseb Assistant Professors, Military Technical college, for their experienced advise, continuous support and deep encouragement through all phases of the work.

Finally, I would like to thank my teachers who helped me in the completion of this work, especially and Dr. fathy abd elkhader. I also place on record, my sense of gratitude to all who, directly or indirectly, have lent their helping hand in this thesis.

#### **ABSTRACT**

The thesis proposes fast, flexible and reasonable development cost system of image enhancement technique using FPGA implementation. Several image enhancement techniques have been surveyed. Afterwards, select some of these techniques to implement using FPGA technology, and then results are analyzed and compared with software simulation results obtained before.

## Research plan:

- 1- Literature survey in FPGA and digital image enhancement techniques.

- 2- Software implementation of the selected image enhancement techniques.

- 3- Hardware implementation of the selected techniques using FPGA.

- 4- Comparative study between the implemented software & hardware image enhancement techniques.

- 5- Conclusions and Future work.

# **Table of Contents**

| Chapter 1: Introduction                                 |    |  |  |

|---------------------------------------------------------|----|--|--|

| Chapter 2: Background and Literature survey             | 3  |  |  |

| 2.1 Introduction                                        |    |  |  |

| 2.2 FPGA Architecture                                   | 3  |  |  |

| 2.3 Logic Elements.                                     | 5  |  |  |

| 2.4 FPGA Development Platform Specifications            | 6  |  |  |

| 2.5 Hardware Implmentation Requirment                   | 7  |  |  |

| 2.6 Programming Languages                               | 9  |  |  |

| 2.6.1 Hardware Description Language (HDL)               | 9  |  |  |

| 2.6.2 Verilog                                           | 10 |  |  |

| 2.6.3 VHDL                                              |    |  |  |

| 2.6.4 AHDL                                              |    |  |  |

| 2.6.5 Handel-C                                          | 11 |  |  |

| 2.7 Quartus II Software                                 |    |  |  |

| 2.8 Simulation Tools                                    |    |  |  |

| 2.9 FPGA Design Flow                                    |    |  |  |

| 2.10 Image enhancement Techniques                       |    |  |  |

| 2.10.1 Image enchantement technique in spatial Domain   |    |  |  |

| 2.10.1.1 Median filter                                  |    |  |  |

| 2.10.1.2 Contrast stretching                            |    |  |  |

| 2.10.1.3 Histogram equalization                         |    |  |  |

| 2.10.1.4 Power-Law transformation                       |    |  |  |

| 2.10.1.5 Negative image transformation                  |    |  |  |

| 2.10.2 Image enchantment techniques in Frequency Domain | 28 |  |  |

| 2.11 Related work for Spatial Domain image enhancement  |    |  |  |

| techniques based on FPGA                                | 30 |  |  |

| Chapter 3: Methodology                                          | 34 |

|-----------------------------------------------------------------|----|

| 3.1 Introduction                                                | 34 |

| 3.2 Software and Hardware Implementation Life Cycle             | 34 |

| 3.3 Hardware Implementation of a Median Filter Algorithm        | 35 |

| Serial input module                                             |    |

| Loading Image process into RAM                                  |    |

| 3.4 Hardware Implementation of Contrast stretching Algorithm    | 41 |

| 3.5 Hardware Implementation of Histogram equalization Algorithm | 43 |

| 3.6 Hardware Implementation of Power Law Transformation         |    |

| Algorithm                                                       | 45 |

| 3.7 Hardware Implementation of Negative Image Transformation    |    |

| Algorithm                                                       | 46 |

|                                                                 |    |

| Chapter 4: Experimental results & Performance evaluation        | 48 |

|                                                                 |    |

| 4.1 Introduction                                                | 48 |

| 4.2 Experimental results using Median Filter                    | 48 |

| 4.3 Experimental results using Contrast stretching              | 52 |

| 4.4 Experimental results using Histogram equalization           | 55 |

| 4.5 Experimental results using Power law transformation         | 59 |

| 4.6 Experimental results using Negative image transformation    | 62 |

| 4.7 Summary                                                     | 65 |

|                                                                 |    |

| Chapter 5: Conclusions and Future work                          | 67 |

|                                                                 |    |

| 5.1 Conclusions                                                 | 67 |

| 5.2 Future work                                                 | 68 |

|                                                                 |    |

| References                                                      | 69 |

|                                                                 |    |

| Appendix                                                        | 72 |

## **List of Abbreviation**

DSP Digital Signal Processor

ASIC Application Specific Integrated Circuits

FPGA Field Programmable Gate Arrays

LE Logic Elements

PROM Programmable Read-Only Memory

LUT Look-Up Table

SRAM Static Random-Access Memory

LAB Logic Array Blocks

HDL Hardware Description Language

VHDL VHSIC Hardware Description Language AHDL Altera Hardware Description Layer

RTL Register Transfer Level

EEPROM Electrically Erasable Programmable Read-Only Memory

S/W Software H/W Hardware

# **List of Figure**

| Figure 2.1  | Basic hardware architecture of FPGA devices                                                      | 4  |

|-------------|--------------------------------------------------------------------------------------------------|----|

| Figure 2.2  | Logic Element block in Cyclone III.                                                              | 5  |

| Figure 2.3  | Categories of Altera FPGA and their technology                                                   | 6  |

| Figure 2.4  | The FPGA product of Altera with a comparison of their technology and cost.                       | 7  |

| Figure 2.5  | Quartus II Development Environment.                                                              | 12 |

| Figure 2.6  | Altera Waveform Simulator.                                                                       | 13 |

| Figure 2.7  | Model-Sim Simulator .                                                                            | 14 |

| Figure 2.8  | FPGA Design Flow Diagram.                                                                        | 16 |

| Figure 2.9  | 3x3 window and Sorting process                                                                   | 18 |

| Figure 2.10 | (a) Original image (b) Image after median filter.                                                | 19 |

| Figure 2.11 | Contrast stretching explanation.                                                                 | 21 |

| Figure 2.12 | Effect of variable the slope E.                                                                  | 22 |

| Figure 2.13 | Histogram equalization for lena image.                                                           | 24 |

| Figure 2.14 | Plots of the equation for different values of $V$ , $c=1$ in all cases.                          | 26 |

| Figure 2.15 | Gamma correction in CRT TV.                                                                      | 27 |

| Figure 2.16 | Negative image of the mammogram.                                                                 | 28 |

| Figure 2.17 | Linear systems.                                                                                  | 30 |

| Figure 2.18 | Sinusoidal shapes which repeat along the x axis: (i) high spatial frequency and (ii) low spatial | 30 |

|             |                                                                                                  |    |

| Figure 3.1  | Function block diagram of the S/W and H/W implementation life cycle.                             | 32 |

| Figure 3.2  | Serial input Module.                                                                             | 34 |

| Figure 3.3  | Loading image from PC to FPGA RAM Module.                                                        | 36 |

| Figure 3.4  | Block Diagam of Median Filter.                                                                   | 37 |

| Figure 3.5  | Schematic Diagram of Median Filter.                                                              | 38 |

| Figure 3.6  | Block Diagram of Contrast stretching.                                                            | 39 |

| Figure 3.7  | Schematic Diagram of Contrast stretching.                                                        | 40 |

| Figure 3.8  | Block Diagram of Histogram Equalization.                                                         | 11 |

| Figure 3.9  | Schematic Diagram of Histogram Equalization.                           | 42 |

|-------------|------------------------------------------------------------------------|----|

| Figure 3.10 | Block Diagram of Power law transformation.                             | 43 |

| Figure 3.11 | Schematic Diagram of Power law transformation.                         | 44 |

| Figure 3.12 | Block Diagram of Negative image transformation.                        | 44 |

| Figure 3.13 | Schematic Diagram of Negative image transformation.                    | 45 |

|             |                                                                        |    |

| Figure 4.1  | Output signals in ModelSim view (Median Filter)                        | 46 |

| Figure 4.2  | Output signals in SignalTap II (Median Filter)                         | 47 |

| Figure 4.3  | Result of Median filter algorithm in Matlab & FPGA processing          | 48 |

| Figure 4.4  | Output signals in ModelSim view (Contrast Stretching)                  | 50 |

| Figure 4.5  | Output signal in SignalTap II (Contrast Stretching)                    | 50 |

| Figure 4.6  | Result of Contrast Stretching algorithm in Matlab & FPGA processing    | 51 |

| Figure 4.7  | Output signals in ModelSim view (Histogram Equalization)               | 53 |

| Figure 4.8  | Output signal in SignalTap II (Histogram Equalization)                 | 53 |

| Figure 4.9  | Result of Histogram Equalization algorithm in Matlab & FPGA processing | 55 |

| Figure 4.10 | 1 0                                                                    | 57 |

| Figure 4.11 | Output signal in SignalTap II (Power Law)                              | 56 |

| Figure 4.12 | Result of Power Law algorithm in Matlab & FPGA processing              | 58 |

| Figure 4.13 |                                                                        | 60 |

| Figure 4.14 | Output signal in SignalTap II (Negative image)                         | 60 |

| Figure 4.15 | Result of Negative image algorithm in Matlab & FPGA                    | 61 |

|             | processing                                                             |    |

# List of Algorithm

| List 2.1   | Median Filter Algorithm                                                                     | 20 |

|------------|---------------------------------------------------------------------------------------------|----|

| List 2.2   | Contrast Stretching Algorithm                                                               | 22 |

| List 2.3   | Histogram equalization Algorithm                                                            | 25 |

| List 2.4   | Power-Law transformation Algorithm                                                          | 27 |

| List 2.5   | Negative image transformation Algorithm                                                     | 28 |

|            | List of Tables                                                                              |    |

| Table 4.1  | Comparison between Altera & Xilinx platform                                                 | 47 |

| Table 4.2  | Comparison results of Median Filter algorithm in different image size                       | 48 |

| Table 4.3  | Comparison results of Median Filter Algorithm                                               | 49 |

| Table 4.4  | Comparison between Altera & Xilinx platform                                                 | 51 |

| Table 4.5  | Comparison results of Contrast Stretching algorithm in different image size                 | 51 |

| Table 4.6  | Comparison results of Contrast Stretching Algorithm                                         | 52 |

| Table 4.7  | Comparison between Altera & Xilinx platform                                                 | 54 |

| Table 4.8  | Comparison results of Histogram Equalization algorithm in different image size              | 54 |

| Table 4.9  | Comparison results of Histogram equalization Algorithm                                      | 56 |

| Table 4.10 | Comparison between Altera & Xilinx platform                                                 | 58 |

| Table 4.11 | Comparison results of Power Law Transformation algorithm in different image size            | 58 |

| Table 4.12 | Comparison results of Power law transformation Algorithm                                    | 59 |

| Table 4.13 | Comparison between Altera & Xilinx platform                                                 | 61 |

| Table 4.14 | Comparison results of Negative Image Transformation algorithm in different image size       | 61 |

| Table 4.15 | Comparison results of Negative image transformation algorithm                               | 62 |

| Table 4.16 | Comparison between implemented algorithms in frequency and logic elements (Altera – Xilinx) | 65 |

# Chapter 1 Introduction

Image Enhancement is a wide area with its applications in different domains. Image Enhancement is a very high computational process; in which processing involves applying a specific function repetitively. One solution to apply this computational process is to use a general-purpose microprocessor or Digital Signal processors. But these implementations are sequential, with less on chip memory for buffering, so we require external memory for buffering. Fetching data from this external memory require certain clock cycles which affect system performance. Also, these systems require a logic element for their operations. We can reduce this logic element and speed up our operations using Application Specific Integrated Circuits (ASICs). But main problems with ASICs, are that they require large time to market, and the initial investments are high. Before developing an ASIC, we require to prototype our design. Field programmable Gate Arrays (FPGAs) prove to be a better solution for rapid prototyping. FPGAs are reprogrammable, have large number of logic cells suitable for implementing image enhancement applications.

This thesis addresses the implementation of image enhancement algorithms like histogram equalization, contrast stretching, negative image transformation, power law transformation, and median filter on FPGA that have become a competitive alternative for high-performance digital signal processing applications. All implemented enhancement algorithms deal with spatial domain techniques, where they enhance low image contrast & remove impulse noise (Salt & paper noise) effectively. All the implementation work has been done in MATLAB 9.0, Quartus II, Xilinx software and DE0 board (Altera) & Spartan3 (Xilinx) [Hardware].

This thesis is organized in five chapters including this one. Chapter 2 introduces FPGA architecture, requirements of the FPGA hardware platform, FPGA design flow and Programming Languages, then background of image enhancement techniques in both spatial domain and frequency domain, and survey on implemented algorithms in spatial domain finally; some related work for Spatial Domain image enhancement techniques based on FPGA is introduced. Chapter 3 also presents software and hardware implementation of a five image enhancement algorithms like processing steps, Block diagram, Schematic diagram, loading image using RS232 and MATLAB code. Chapter 4 is going to show the performance analysis of the proposed hardware design in terms of computation speed, power consumption, and number of logic element in both (Altera - Xilinx) boards. In Chapter 5, the conclusion and future work discuss the thesis and all the work done. Further improvements and other ideas are suggested.

# Chapter 2 Background and Literature survey

#### 2.1 Introduction

This Chapter will introduce a background material relevant to the subject of this thesis. It begins by briery outlining FPGA architecture, FPGA design flow and Programming Languages. We then provide relevant technical details of image enhancement techniques in both spatial domain and frequency domain and survey on implemented algorithms in spatial domain used in this research. Finally we will outline related previous work for Spatial Domain image enhancement techniques based on FPGA.

#### 2.2 FPGA Architecture

The Field Programmable Gate Array (FPGA) is a semiconductor device that can be programmed after manufacturing. We can use an FPGA to implement any logical function that an application-specific integrated circuit (ASIC) could perform, but the ability to update the functionality after shipping offers advantages for many applications [1].

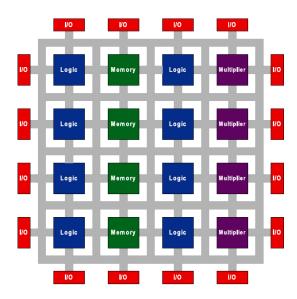

The general architecture of FPGA is given in Figure 2.1. It consists of an array of programmable logic blocks of different types, including general logic, memory and multiplier blocks, surrounded by a programmable routing fabric that allows blocks to be programmable interconnected.

The array is surrounded by programmable input/output blocks, labeled I/O in the figure, that connect the chip to the outside world. The "programmable" term in FPGA indicates an ability to program a function into the chip after silicon fabrication is complete.

Figure 2.1 Basic hardware architecture of FPGA devices [2]

This change in function is made possible by the programming technology, which is a method that can cause a change in the behavior of the prefabricated chip after fabrication.

Unlike previous generation of FPGAs using I/Os with programmable logic and interconnects, today's FPGAs consist of various mixes of configurable embedded SRAM, high-speed transceivers, high-speed I/Os, logic blocks, and logic elements [1].

An FPGA contains a large number of logic elements (LE) that can be wired according to a logic function specified by a user defined code. Each element is interconnected by a matrix of wires and programmable switches. This is done by a user program that defines the function of the circuit, using a hardware description language such as Verilog or VHDL.

We can configure LE to perform complex combinational functions, or simple logic gates like AND, OR and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flip flops or more complete blocks of memory.