# FPGA IMPLEMENTATION OF TIMING RECOVERY IN DVB-T2

By

Eng. / Sherif Maher Saad Elewa

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE

in

Electronics and Communications Engineering

# FPGA IMPLEMENTATION OF TIMING RECOVERY IN DVB-T2

By

Eng. / Sherif Maher Saad Elewa

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

Electronics and Communications Engineering

Under the Supervision of

Associate Prof. Dr. Ahmed F. Shalash

.....

Associate Professor of Communications

Electronics and Communications

Engineering

Faculty of Engineering, Cairo University

# FPGA IMPLEMENTATION OF TIMING RECOVERY IN DVB-T2

By Eng. / Sherif Maher Saad Elewa

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

**Electronics and Communications Engineering**

Approved by the

Examining Committee

Associate Prof. Dr. Ahmed F. Shalash, Thesis Main Advisor

Prof. Dr. Mohamed H. Nafie, Internal Examiner

Prof. Dr. El Sayed M. Saad, External Examiner

- Faculty of Engineering Helwan University

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2017 **Engineer's Name:** Sherif Maher Saad Elewa

**Date of Birth:** 10/07/1988 **Nationality:** Egyptian

E-mail: sherif.maher@ymail.com

Phone: +2 01007045066 Address: +2 01007045066 El Haram, Giza, Egypt

**Registration Date:** 01/10/2012 **Awarding Date:** 01/10/2017

**Degree:** Master of Science

**Department:** Electronics and Communications Engineering

**Supervisors:**

Associate Prof. Dr. Ahmed F. Shalash

**Examiners:**

Prof. Dr. El Sayed M. Saad (External examiner)

Prof. Dr. Mohamed H. Nafie (Internal examiner)

Assoc. Prof. Dr. Ahmed F. Shalash (Thesis main advisor)

### **Title of Thesis:**

FPGA Implementation Of Timing Recovery In DVB-T2

### **Key Words:**

Digital Video Broadcasting; Synchronization; FPGA; Correlation; Sampling Frequency Offset

#### **Summary:**

DVB-T2 received signal, being an OFDM signal, suffers from timing errors. The broad objective of this study is to illustrate how to recover the time for the DVB-T2 received signal. This is done using robust algorithms divided on two main stages. Firstly, the accurate start of the frame detection. Secondly, the sampling frequency offset detection and correction. The hardware implementation for the proposed system is presented using some methods to reduce the hardware complexity keeping the performance. The RTL implementation is simulated on Modelsim and tested on Altera Stratix III device.

## Acknowledgements

All words of praise and glory to ALLAH the one and only one almighty God, without support from ALLAH nothing can be accomplished. ALLAH is the most kind and the most merciful.

I would like to express my deep regards and appreciation to my thesis supervisor Dr. Ahmed F. Shalash for his passionate guidance and continuous help. This dissertation could not be completed without his effective influence and valuable suggestions.

I owe a debt of heartfelt gratitude to my family for their continuous encouragement, constant prayers and ultimate support. For this and much more, I dedicate this thesis to them.

Lastly, but not least, I would like to thank my professors who helped throughout my study and research.

## **Table of Contents**

| Acknowledgements |                 |                                                             | j   |  |  |  |  |  |

|------------------|-----------------|-------------------------------------------------------------|-----|--|--|--|--|--|

| Li               | st of '         | Tables                                                      | iv  |  |  |  |  |  |

| Li               | List of Figures |                                                             |     |  |  |  |  |  |

| No               | omen            | clature                                                     | vii |  |  |  |  |  |

| Al               | ostrac          | t                                                           | ix  |  |  |  |  |  |

| 1                | Introduction    |                                                             |     |  |  |  |  |  |

|                  | 1.1             | DVB-T2 System Overview                                      | 1   |  |  |  |  |  |

|                  |                 | 1.1.1 DVB-T2 Frame Structure                                | 2   |  |  |  |  |  |

|                  |                 | 1.1.2 P1 Symbol Structure                                   | 3   |  |  |  |  |  |

|                  |                 | 1.1.3 Frequency Domain P1 Symbol                            | 3   |  |  |  |  |  |

|                  |                 | 1.1.4 Time Domain P1 Symbol                                 | 5   |  |  |  |  |  |

|                  |                 | 1.1.5 DVB-T2 Pilots                                         | 6   |  |  |  |  |  |

|                  |                 | 1.1.5.1 Scattered Pilots                                    | 6   |  |  |  |  |  |

|                  |                 | 1.1.5.2 Continual Pilots                                    | 8   |  |  |  |  |  |

|                  |                 | 1.1.5.3 Edge Pilots                                         | 8   |  |  |  |  |  |

|                  |                 | 1.1.5.4 P2 Pilots                                           | 9   |  |  |  |  |  |

|                  |                 | 1.1.5.5 Frame Closing Pilots                                | 9   |  |  |  |  |  |

|                  | 1.2             | System Time and Frequency Errors                            | 10  |  |  |  |  |  |

|                  | 1.3             | Thesis Objectives                                           | 10  |  |  |  |  |  |

|                  | 1.4             | Organization of the thesis                                  | 11  |  |  |  |  |  |

| 2                |                 | ing Errors                                                  | 12  |  |  |  |  |  |

|                  | 2.1             | Introduction                                                | 12  |  |  |  |  |  |

|                  |                 | 2.1.1 Frame Delay                                           | 12  |  |  |  |  |  |

|                  |                 | 2.1.2 SFO Error                                             |     |  |  |  |  |  |

|                  | 2.2             | Related work                                                | 14  |  |  |  |  |  |

|                  |                 | 2.2.1 Start of the Frame Detection (Coarse Synchronization) |     |  |  |  |  |  |

|                  |                 | 2.2.2 SFO Detection and Correction (Fine Synchronization)   | 17  |  |  |  |  |  |

| 3                | Frai            | ne Synchronization                                          | 21  |  |  |  |  |  |

|                  | 3.1             | Maximum Likelihood Algorithm                                |     |  |  |  |  |  |

|                  | 3.2             | Complexity Reduction                                        |     |  |  |  |  |  |

|                  | 3.3             | Proposed Architecture                                       |     |  |  |  |  |  |

|                  | 3.4             | Complexity Comparison                                       | 26  |  |  |  |  |  |

| 4                |                 | A Implementation of Frame Synchronization                   | 28  |  |  |  |  |  |

|                  | 4.1             | Modified Maximum Likelihood Algorithm                       | 28  |  |  |  |  |  |

|                  | 4.2             | Hardware Implementation Of The MML Estimator                |     |  |  |  |  |  |

|                  |                 | 4.2.1 Delay Element                                         | 30  |  |  |  |  |  |

|      |        | 4.2.2   | Conventional Complex Multiplier                       | 30 |

|------|--------|---------|-------------------------------------------------------|----|

|      |        | 4.2.3   | Complex Conjugate Multiplier                          |    |

|      |        | 4.2.4   | Running Average Filter (RAF)                          |    |

|      |        | 4.2.5   | Search Engine                                         |    |

|      |        | 4.2.6   | Phase Calculation                                     |    |

|      | 4.3    | Fixed 1 | Point Configuration                                   |    |

|      |        | 4.3.1   | Synthesis and Timing Results                          |    |

| 5    | SFO    | Detect  | ion and Correction                                    | 36 |

|      | 5.1    | SFO D   | Detection                                             | 36 |

|      | 5.2    | SFO C   | Correction                                            | 38 |

|      |        | 5.2.1   | Farrow Structure                                      | 38 |

|      |        | 5.2.2   | Multi Rate Farrow Structure                           | 41 |

|      |        | 5.2.3   | FDF Implementation                                    | 43 |

|      |        | 5.2.4   | FDF Complexity Reduction                              | 44 |

|      | 5.3    | Compl   | lexity Comparison                                     | 48 |

| 6    | Imp    | lementa | ation Results                                         | 49 |

|      | 6.1    | Integra | nted System                                           | 49 |

|      | 6.2    | Simula  | ation Results                                         | 49 |

|      |        | 6.2.1   | Frame Synchronization Software Simulation             | 49 |

|      |        | 6.2.2   | Frame Synchronization Hardware Simulation             | 52 |

|      |        |         | 6.2.2.1 Hardware Performance                          | 53 |

|      |        | 6.2.3   | SFO Detection and Correction Simulation               | 54 |

| Di   | scuss  | ion and | Conclusions                                           | 57 |

| Re   | eferen | ces     |                                                       | 58 |

| Αį   | pend   | ix A F  | Frame Start Derivation                                | 62 |

| Δı   | nend   | iv R V  | Verilog Code Of Modified Maximum Likelihood Algorithm | 66 |

| · -1 | В.1    |         | p level module                                        |    |

|      | B.2    |         | lex conjugate multiplier                              |    |

|      | B.3    | _       | al complex multiplier                                 |    |

|      | B.4    |         | ng average filter                                     |    |

|      | B.5    |         | ctor of RAF                                           |    |

|      | B.6    |         | nulator of RAF                                        |    |

|      | B.7    |         | by N                                                  |    |

|      | B.8    | •       | er with variable width                                |    |

|      |        | _       | e magnitude block                                     | 87 |

## **List of Tables**

| 1.1  | SI Field of PI Symbol                                                      | 3  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | S1 With S2 For Non-T2                                                      | 4  |

| 1.3  | S2 Field of P1 Symbol                                                      | 5  |

| 1.4  | Presence of the various types of pilots in each type of symbol             | 6  |

| 1.5  | Scattered pilot pattern in SISO mode                                       | 6  |

| 1.6  | Scattered pilot pattern in MISO mode                                       | 7  |

| 1.7  | Scattered pilot separations                                                | 7  |

| 1.8  | Amplitudes of the scattered pilots                                         | 8  |

| 1.9  | Continual Pilot groups used with each FFT size                             | 8  |

| 1.10 | Amplitudes of the continual pilots                                         | 8  |

| 1.11 | Amplitudes of the P2 pilots                                                | 9  |

| 1.12 | Combinations of FFT size, guard interval and pilot pattern for which frame |    |

|      | closing symbols are used in SISO mode                                      | 9  |

| 3.1  | The Proposed Search Algorithm                                              | 26 |

| 3.2  |                                                                            | 27 |

| 4.1  | Hardware Utilization                                                       | 35 |

| 4.2  |                                                                            | 35 |

| 5.1  | Farrow Filter Coefficients For Cubic Polynomial                            | 43 |

| 5.2  |                                                                            | 44 |

| 5.3  | Timing Sequence Of Cubit FDF                                               | 46 |

| 5.4  | FDF Complexity Comparison                                                  |    |

# **List of Figures**

| 1.1  | DVB-T2 Frame Structure                                       | 2        |

|------|--------------------------------------------------------------|----------|

| 1.2  | P1 Symbol Structure                                          | 6        |

| 1.3  | Scattered Pilots Separation                                  |          |

| 2.1  | Frame Delay                                                  | 13       |

| 2.2  | Effect of SFO on Sampled Signal                              | 13       |

| 2.3  | Effect of 20 PPM SFO on the 16-QAM Received Signal After FFT | 14       |

| 2.4  | CBS Structure                                                | 15       |

| 2.5  | Correlation For The P1 Detection                             | 15       |

| 2.6  | Modified CBS                                                 | 16       |

| 2.7  | Modified CBS Correlation Waveform                            | 16       |

| 2.8  | Slope Based Synchronization Scheme                           | 17       |

| 2.9  | Maximum Likelihood Scheme                                    | 17       |

| 2.10 | Continuous-time Feedback Synchronizer                        | 18       |

|      | Digital Receiver with Non-synchronized Sampling              | 18       |

|      | Third Order Lagrange Interpolation                           | 19       |

|      | Fourth Order Lagrange Interpolation                          | 19       |

|      | Basic Wide Bandwidth Variable Fractional Delay Scheme        | 20       |

| 3.1  | P1 Symbol Regions                                            | 21       |

| 3.2  | The Output of the Correlator for C-part and B-part           | 24       |

| 3.3  | Block Diagram of the Proposed ML Time Estimator Scheme       | 25       |

| 3.4  | The Output of the Proposed ML Time Estimator Scheme          | 25       |

| 3.5  | The Block Diagram Of The Estimator                           | 26       |

| 4.1  |                                                              | 28       |

| 4.1  | Block Diagram of the Proposed ML Time Estimator              | 20<br>29 |

| 4.2  | Block Diagram of the Proposed ML whole Estimator             | 30       |

| 4.4  | Block Diagram Of Conventional Complex Multiplier             |          |

| 4.5  | Block Diagram Of Complex Complex Multiplier                  | 31       |

| 4.6  | Block Diagram Of Running Average Filter                      | 31       |

| 4.7  | Block Diagram Of Search Engine                               |          |

| 4.7  | Block Diagram Of Altera Fixed Point Divider                  | 33       |

| 4.9  | Block Diagram Of Altera Arctan                               | 33       |

|      |                                                              | 33<br>34 |

|      | Block Diagram of RAF Rounder                                 | 35       |

|      |                                                              |          |

| 5.1  | The Absolute Value of the Cross Correlation                  | 37       |

| 5.2  | The Farrow Structure                                         | 39       |

| 5.3  | Input/Output Samples Of FDF                                  | 39       |

| 5.4  | The FDF of Farrow Structure                                  | 39       |

| 5.5  | Poly-phase Structure Of M+1 <sup>th</sup> FIR Filter         | 40       |

| 5.6  | The Multi-rate Farrow Structure                              | 41       |

| 5.7  | The Power Spectral Density Of The Input Signal               | 41       |

| 5.8  | The Power Spectral Density Of The Up Sampled Signal    |

|------|--------------------------------------------------------|

| 5.9  | The Power Spectral Density Of The Signal After The HBF |

| 5.10 | Cubic Order FDF (Direct Implementation)                |

| 5.11 | FDF First Complexity Reduction                         |

| 5.12 | FDF Second Complexity Reduction                        |

| 5.13 | FDF Third Complexity Reduction                         |

| 5.14 | FDF Fourth Complexity Reduction                        |

| 6.1  | The Proposed Architecture of the Timing Recovery       |

| 6.2  | Mean Square Error vs SNR in AWGN channel               |

| 6.3  | CFO Error vs SNR in AWGN channel                       |

| 6.4  | Mean Square Error vs SNR in two-taps channel           |

| 6.5  | CFO Error vs SNR in two-taps channel                   |

| 6.6  | Mean Square Error vs SNR for Two Tap Channel           |

| 6.7  | MATLAB vs. Hardware Results                            |

| 6.8  | ModelSim Simulation Wave                               |

| 6.9  | Tracking the SFO Error                                 |

| 6.10 | The Received Constellation After Recovery              |

### **Nomenclature**

$L_{data}$  number of data symbols

$N_{P2}$  number of P2 symbol

$N_{T2}$  number of T2-frames

$T_F$  duration of one T2-frame

$T_{P1}$  duration of the P1 symbol

$T_{SF}$  duration of one super-frame

$T_S$  duration of one OFDM symbol

ADC analog to digital converter

AWGN additive white Gaussian noise

BCH Bose-Chaudhuri-Hocquenghem

CBS correlation based synchronization

CFO carrier frequency offset

CM complex multipliers

COFDM Coded orthogonal frequency division multiplexing

DBPSK differential binary phase shift keying

DFT discrete Fourier transform

DVB-T terrestrial digital video broadcasting first generation

DVB-T2 terrestrial digital video broadcasting second generation

FDF fractional delay filter

FEC Forward error correction

FEF Future Extension Frame

FFT fast Fourier transform

FIR finite impulse response

HBF half band filter

ICI inter carrier interference

ISI inter symbol interference

LDPC low density parity check

LLF log-likelihood function

LSB least significant bit

MISO multiple input single output

ML maximum likelihood

MSB most significant bits

NCO numerical controlled oscillator

OFDM orthogonal frequency division multiplexing

PDF probability density function

PLL phase locked loop

PLPs piped physical layers

PML pseudo maximum likelihood

PP pilot patterns

PPM part per million

QAM quadrature amplitude modulation

QPSK quadrature phase-shift keying

RAF running average filter

RNE Rounding to nearest even

RTL register transfer level

SBS slope based synchronization

SFO sampling frequency offset

SISO single input single output

SNR signal to noise ratio

STO symbol time offset

### **Abstract**

OFDM signals are sensitive to sample timing errors, causing both phase errors and sample duration offset. Sample duration errors causes loss of orthogonality between sub-carriers. As a result, inter-carrier interference is introduced, which causes destruction to the received signal. On the other hand, phase errors lead to wrong interpretation of the received symbols. Both types of errors degrade the system performance by increasing the bit error rate.

The second generation terrestrial digital video broadcasting (DVB-T2), being a wireless OFDM system, suffers from these time errors. A sampling frequency offset is introduced in the received signal due to the difference between the transmitter and receiver oscillators. This offset will be accumulated and finally turns into an integer and fraction offset in the received symbols. In addition, there is a time shift at the start of the received frame due to the delay of the channel itself. The DVB-T2 standard provides a specific symbol, called P1 symbol located at the start of the frame, in order to facilitate the time estimation process by identifying the correct start of the frame. Also, it is used in the coarse frequency estimation by detecting the fractional part of the carrier frequency offset. In addition, several pilots are presented inside the DVB-T2 frame to be used in the detection and synchronization purposes.

In this work, the P1 symbol will be exploited to estimate the correct start of the frame. This will be achieved via correlation using the maximum likelihood estimation mechanism to reach the highest accuracy. However, the complexity of this scheme is prohibited, thus, a smart mathematical deduction is followed to reduce the hardware implementation complexity.

In addition, asynchronous time tracking is achieved using two types of pilots (scattered pilots, and continual pilots) to track the sampling frequency offset. The tracking is done via fixed sampling rate at the beginning of the receiver. Then, a correlation with the previous mentioned pilots in time domain is performed to estimate the variance in the sampling offset. Finally, the correction is achieved by interpolation and decimation via multi-rate Farrow structure. The hardware implementation complexity is reduced by reordering and eliminating some unused blocks.

At the end of this work, we will be able to recover the time of the received DVB-T2 frame. The proposed architecture is a fast tracking loop with reduced hardware complexity and robust against noise under bad channel conditions.

Finally, the proposed system is tested for the effect of the carrier frequency offset errors to be sure that the system is not affected by such error. Finally the system is implemented with Verilog 2001 and simulated under Modelsim and gave the same performance as that of MATLAB model. We verify the functionality and the design of the RTL implementation by generating test vectors based on the MATLAB fixed point model and cross check it with the RTL data. The implementation is targeting the Altera Stratix III EP3SL150F1152C2N FPGA device.

## **Chapter 1: Introduction**

The terrestrial digital video broadcasting second generation (DVB-T2) is one of the most important and modern applications of the orthogonal frequency division multiplexing (OFDM) systems. However, being an OFDM system makes it vulnerable to time and frequency offsets and synchronisation errors. Thus, a timing recovery is needed to recover the received data and maintain the time synchronization. Hence, the DVB-T2 standard provides some pilots and preambles to facilitate the estimation of these offsets. In order to appreciate the challenges and introduce the solution, a discussion of the DVB-T2 system characteristics is needed. Then, in view of these characteristics, different problems are introduced in order to show the difficulties facing the DVB-T2 signal. The rest of this chapter discussed the thesis objectives and organization.

### 1.1 DVB-T2 System Overview

The terrestrial digital video broadcasting first generation (DVB-T) standard presented a very powerful digital television transmission system. This digital communication chain is developed based on quadrature amplitude modulation (QAM), robust forward error correction, and fast Fourier transform (FFT). Exploiting these communication techniques makes DVB-T very powerful digital communication system which immune to transmission errors and bad channel conditions. Recently, the second generation of the DVB standard has been emerged. The DVB-T2 standard providing a renovation of the terrestrial video transmission. DVB-T2 achieves a capacity increase of 50% over the old digital television DVB-T system [36]. Moreover, DVB-T2 is more suitable for mobile reception compared to the DVB-T which is originally developed for static and portable devices. DVB-T2 incorporates flexible physical layer structure. DVB-T2 employ new higher order modulation ranging from quadrature phase-shift keying (QPSK) to the newly introduced 256 QAM. The DVB-T2 also introduces larger range of options in FFT sizes starting with 1 K up to 32 K subcarriers. Each FFT size has a flexible set of guard intervals, bandwidth and pilot patterns to enable better spectral efficiency and adaptation to different terrestrial link conditions. Innovative error correction schemes have been introduced in the form of concatenated Bose-Chaudhuri-Hocquenghem (BCH) code and low density parity check (LDPC) code. In addition, flexible time interleaving and the introduction of the concept of piped physical layers (PLPs) improve the mobile performance of the DVB-T2 all add up to enhance the deployment of DVB-T2 in mobile devices.

All the above features add to the value of DVB-T2 physical layer. However, it becomes a challenge to incorporate those sets of features in a high performance decoder while preserving the compact size and low power mandated by mobile applications [7].

DVB-T2 characteristics are:

- Coded orthogonal frequency division multiplexing (COFDM) modulation with QPSK, 16-QAM, 64-QAM, or 256-QAM constellations.

- OFDM modes are 1k, 2k, 4k, 8k, 16k, and 32k. The symbol length for 32k mode is about 4 ms.

- Guard intervals are 1/128, 1/32, 1/16, 19/256, 1/8, 19/128, and 1/4. (For 32k mode, the maximum is 1/8.)

- Forward error correction (FEC) is concatenated LDPC and BCH codes, with rates 1/2, 3/5, 2/3, 3/4, 4/5, and 5/6.

- There are scattered pilots with 8 different pilot patterns (PP). Also, there are continual, edge, P2, and frame-closing pilots.

- In case of 32k OFDM mode, a larger part of the standard 8 MHz channel can be used, adding about 2% extra capacity.

- The available channel bandwidths for the DVB-T2 signal are 1.7, 5, 6, 7, 8, and 10 MHz.

- The available transmission modes are single input single output (SISO) and multiple input single output (MISO) [6]. Recently, DVB-T2 system adopted MISO in order to provide high definition television [1, 2].

- Multiple PLP to enable service specific robustness.

### 1.1.1 DVB-T2 Frame Structure

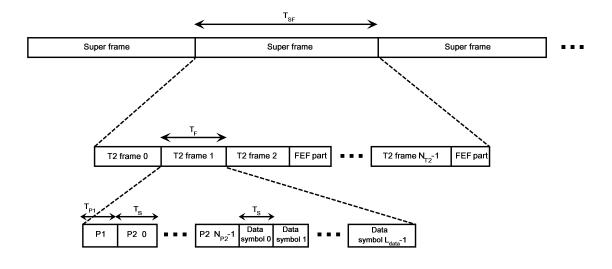

The DVB-T2 frame structure consists of super-frames which split into number of T2-frames ( $N_{T2}$ ), and may sometimes contain Future Extension Frame (FEF) parts. These T2-frames are divided into some OFDM symbols. Each T2-frame begins with one OFDM symbol called P1 symbol. Then, there are number of P2 symbol ( $N_{P2}$ ) right after the P1 symbol. The rest of the T2-frame are number of data symbols ( $L_{data}$ ) as shown in Figure 1.1. These data symbols consist of normal symbols and one frame closing symbol located at the end of each frame to mark the end of the T2 frame. The duration of one super-frame ( $T_{SF}$ ), and the duration of one T2-frame ( $T_{SF}$ ). The duration of one OFDM symbol ( $T_{S}$ ), and the duration of the P1 symbol ( $T_{P1}$ ).

Figure 1.1: DVB-T2 Frame Structure