# **Ain Shams University Faculty of Engineering**

### **Electronics and Communication Engineering Department**

### **A Compact Model for Nanoscale Transistors**

#### **A THESIS**

Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

By

### **Ahmed Fathy Abo-Elhadeed Hassan**

B.Sc. in Electrical Engineering (Electronics and Communication Engineering) Ain Shams University - 2005

Supervised by:

Prof. Dr. Hani Fikry Ragai

Ain Shams University

Prof. Dr. Wael Fikry Farouk

Ain Shams University

Dr. Tarek Mohammad Abdolkader

Benha University

Cairo, 2010

**STATEMENT**

This thesis is submitted to Ain Shams University in partial fulfillment of the

requirements for the degree of Master of Science in Electrical Engineering.

The work included in the thesis was carried out by the author at the Electronics

and Communication Engineering Department, Faculty of Engineering, Ain Shams

University, Cairo, Egypt.

No part of this thesis has been submitted for a degree or a qualification at any

other university or institute.

Name: Ahmed Fathy Abo-Elhadeed Hassan

**Signature:**

Date:

ii

# **CURRICULUM VITAE**

Name of Researcher Ahmed Fathy Abo-Elhadeed Hassan

**Date of Birth** 11/05/1983

**Place of Birth** Cairo

First University Degree B.Sc. in Electrical Engineering

Name of University Ain Shams University

**Date of Degree** June 2005

### **ABSTRACT**

Ahmed Fathy Abo-Elhadeed Hassan, "A Compact Model for Nanoscale Transistors", Master of Science dissertation, Ain Shams University, 2009.

Down-scaling of MOS devices is continuously attempted aiming to achieve faster circuit speed, smaller area, and lower power dissipation. Multi-gate MOSFET is one of the most promising semiconductor devices that was proven to be the best choice for future ICs, so, it has become an intense subject of scientific research.

This thesis addresses the different multi-gate structures and the recent compact models of the double gate structure. In this work, we study the physical effects of multigate MOSFETs. Moreover we review the different compact models of double-gate MOSFETs (Taur, Ortiz, Hu and Common Symmetric Multi-Gate models) stressing the advantages and disadvantages of each model. Finally, we introduce a new model based on Hu's model. Our new model introduces by a simple way modifying the energy states quantization effect without the need to solve Schrödinger's equation. In addition, we present how to include the velocity saturation, channel length and drain induced barrier lowering effects. These effects represent the most important short channel effects. Furthermore, we show an extraction flow to extract our proposed model parameters. We use the Nanomos device simulator results as a reference to apply our extraction flow. Finally, we validate the model continuity and compare its results with Hu's model.

**Key Words**: double gate MOSFETS, compact models, quantum confinement effect, short channel effects

### ACKNOWLEDGMENT

I would like first to thank my supervisors Prof. Dr. Hani Fikry Ragai, Prof. Dr. Wael Fikry Farouk and Dr. Tarek Mohammad Abdolkader for their continuous guidance, encouragement, help and patience. I learnt so many valuable things from them.

I would be ungrateful if I fail to express my sincere gratitude and appreciation to Prof. Dr. Wael Fikry Farouk for all what he has given to me from his noteworthy experience and knowledge. I always like to consult him in all my life subjects as I consider him like my father not only my teacher. He is my role model who affects deeply my personality. I wish that I could follow his footsteps to be such great person.

I would like also to thank my uncle Mahmoud Abdolrahim for his great support to me through my whole life. I would like to thank him for his continuous encouragement and sincere care. He treats me like a son; He always guides and helps me to solve any problems I face.

I would like to thank my dear friend Yasser Sabry for his cooperation and help during this work. His discussions were very great and helped me to finish my work.

Finally I would like to thank my father, mother, sister and wife for their constant encouragement and support throughout the years. Their confidence in my abilities and their encouragement has really helped me get through all the difficulties I encountered during this work.

# **Table of Contents**

| List of Figures                                            | vii |

|------------------------------------------------------------|-----|

| List of Tables                                             | X   |

| List of Symbols                                            | xi  |

| Introduction                                               | 1   |

| Chapter 1: Literature Review                               |     |

| 1.1 Introduction                                           |     |

| 1.2 MOSFET scaling challenges                              |     |

| 1.3 Multi Gate MOSFETs                                     |     |

| 1.3.1 Single Gate SOI MOSFETs                              |     |

| 1.3.2 Double-gate MOSFETs                                  | 12  |

| 1.3.3 Other Multi-gate MOSFET Structures                   |     |

| 1.4 Gate Geometry and Electrostatic Integrity              |     |

| 1.5 Quantum effects in double-gate MOSFETs                 |     |

| 1.5.1 Quantum confinement.                                 |     |

| 1.5.2 Volume inversion.                                    |     |

| 1.6 Conclusion                                             |     |

| Chapter 2: Double-Gate Compact Models                      | 26  |

| 2.1 Introduction                                           |     |

| 2.2 Compact Models                                         |     |

| 2.3 Double-gate compact models                             |     |

| 2.3.1 Taur Model                                           | 29  |

| 2.3.2 Ortiz Model                                          | 33  |

| 2.3.3 Hu Model                                             | 40  |

| 2.3.4 Common Symmetric Multi-Gate Model                    | 45  |

| 2.4 Device Simulation                                      | 47  |

| 2.4.1 Advantages of Device Simulation                      | 48  |

| 2.4.2 The Basic Elements of Device Simulation              | 48  |

| Chapter 3: Compact Model for Undoped Symmetric Double Gate | 51  |

| 3.1 Introduction                                           | 51  |

| 3.2 Proposed DC Model                                      |     |

| 3.3 Parameter Extraction                                   | 55  |

| 3.4 Model validation                                       | 62  |

| 3.4.1 Model results                                        | 63  |

| 3.4.2 Model performance                                    | 76  |

| Conclusions and Future Work                                |     |

| References                                                 | 84  |

# **List of Figures**

| Figure 1. 1 Moore's Law in microprocessors.                                                      | . 2      |

|--------------------------------------------------------------------------------------------------|----------|

| Figure 1. 2 The depletion-layer charge distribution for bulk MOSFET                              | . 3      |

| Figure 1. 3 Surface potential in the channel for devices with different channel lengths          |          |

| and biases [3].                                                                                  | . 4      |

| Figure 1. 4 Magnitude of carrier velocity in the inversion layer versus magnitude of             |          |

|                                                                                                  | . 5      |

| Figure 1. 5 (a) Experimental drain characteristics for a short channel MOSFET ( $L_{eff} = 2$    | 2.7      |

| μm), (b) Characteristics calculated from long-channel theory [4]                                 | . 5      |

| Figure 1. 6 Gate oxide thickness (nm) versus technology node (nm) [5]                            | . 6      |

| Figure 1. 7 Energy band diagrams illustrating (a) FNT and (b) DT.                                | . 7      |

| Figure 1. 8 Measured (dots) and simulated (solid lines) tunneling currents in thin-oxide         |          |

| polysilicon-gate MOS devices. The dashed line indicates a tunneling current level of             |          |

| L - J                                                                                            | . 7      |

| Figure 1. 9 Graph showing the dielectric constants (and variations) of different high-k          |          |

| gate material candidates as reported in the literature [11].                                     |          |

| Figure 1. 10 Cross-section of bulk and SOI MOS devices.                                          | . 9      |

| Figure 1. 11 Kink effect in the output characteristics of a PD-SOI MOSFET in deep                |          |

|                                                                                                  | 11       |

| Figure 1. 12 Drain current drain voltage of the SOI NMOS device with a front gate                |          |

| oxide of 7nm, a thin film of 80nm, a buried oxide of 400nm, a channel length of $0.2~\mu m$      |          |

| and a channel width of 9.5 µm, considering the energy transport and the lattice                  | 1 1      |

| temperature [4]                                                                                  | 11       |

| <b>Figure 1. 13</b> Examples of double-gate MOSFET structure: A: DELTA MOSFET; B: FinFET.        | 1 2      |

|                                                                                                  | 12<br>13 |

| Figure 1. 15 The effect of electric field lines from source and drain on the channel region      |          |

| in different types of MOSFETs: A: Bulk MOSFET; B: Fully depleted SOI MOSFET; C                   |          |

| Fully depleted SOI MOSFET with thin buried oxide and ground plane; D: Double gate                | •        |

| MOSFET [31]                                                                                      | 14       |

| <b>Figure 1. 16</b> Electrostatic Integrity in A: bulk, B: fully depleted SOI and C: double-gate |          |

|                                                                                                  | 15       |

| <b>Figure 1. 17</b> Typical drain-induced barrier lowering in bulk, fully depleted SOI and       |          |

| double-gate MOSFETS calculated by MASTAR [34].                                                   | 16       |

| <b>Figure 1. 18</b> Evolution of gate length predicted by the 2005 ITRS for high-performance     |          |

| (HP), low operating power (LOP), and low standby power (LSTP) digital circuits [31].             |          |

| Figure 1. 19 Simulated threshold voltage roll-off for double-gate MOSFET with                    |          |

| tox=1.5nm and $1nm$ . The silicon channels are undoped [35].                                     | 18       |

| <b>Figure 1. 20</b> Simulated DIBL for undoped double-gate MOSFET with $tox=1.5nm$ and           |          |

| <i>1nm</i> [35]                                                                                  |          |

| Figure 1. 21 The subthreshold swing at different effective channel lengths for both bulk         | -        |

| and                                                                                              | 19       |

| Figure 1. 22 Average values of the electric field and carrier mobility versus gate voltage       |          |

| for 3 nm thick transistor (DG and SG modes) [36].                                                | 20       |

| <b>Figure 1. 23</b> Schematic illustrating band-to-band tunneling in a reverse biased p-n                  |    |

|------------------------------------------------------------------------------------------------------------|----|

| junction                                                                                                   |    |

| Figure 1. 24 Double-gate MOSFET.                                                                           | 21 |

| <b>Figure 1. 25</b> Energy band diagram in the transverse direction of DG MOSFET of Fig. 1.24              |    |

| Figure 1. 26 Energy gap widening and the splitting of the conduction band into subba                       |    |

| due to carrier confinement.                                                                                |    |

| <b>Figure 1. 27</b> Threshed voltage dependence on silicon layer thickness [38]                            |    |

| Figure 1. 28 Electron concentration profile in double-gate MOSFETs with different                          |    |

| silicon film thickness values [41].                                                                        | 24 |

| Figure 1. 29 Electron mobility in a double-gate transistor versus the silicon film                         |    |

| thickness.                                                                                                 | 24 |

| <b>Figure 2. 1</b> Step-by-step guide for developing a Compact Model [43]                                  | 28 |

| Figure 2. 2 (a) Schematic diagram of a DG MOSFET. V(y) is the quasi-Fermi potential                        |    |

| a point in the channel. $\beta$ is a function of V. (b) Band diagram along a vertical cut (AA              |    |

| (a). The potential (x; y) is defined as the intrinsic Si (midgap) level referenced to the                  |    |

| Fermi level of the $n^+$ source as shown (so that $n = n_i$ where $\psi = 0$ )                             | 30 |

| Figure 2. 3 $I_{ds} - V_{ds}$ curves calculated from the analytic model (solid curves), compar             | ed |

| with the 2-D numerical simulation results (open circles).                                                  | 33 |

| Figure 2. 4 Undoped-body symmetric DG n-MOSFET channel potential within the                                |    |

| channel thickness, at two gate voltage biases, (top) below threshold, and (bottom) abo                     | ve |

| threshold                                                                                                  |    |

| <b>Figure 2. 5</b> Surface potential, $\psi_s$ , (continuous lines) and potential extremum (at the         |    |

| center of the channel), $\psi_0$ , (broken lines) versus gate voltage.                                     | 37 |

| Figure 2. 6 The basic elements of semiconductor device simulation.                                         | 50 |

| Figure 3. 1 Schematic structure of a symmetric DG n-MOSFET                                                 | 52 |

| Figure 3. 2 Devices used in the extraction flow.                                                           |    |

| Figure 3. 3 $I_{ds}$ versus $V_{gs}$ at low $V_{ds}$ .                                                     |    |

| Figure 3. 4 $I_{ds}$ versus $V_{ds}$ at different $V_{gs}$                                                 |    |

| Figure 3. 5 Threshold voltage versus length at low $V_{ds}$ for the largest silicon thickness              |    |

| Figure 3. 6 Threshold voltage versus length at high $V_{ds}$ for the largest silicon thickness             |    |

|                                                                                                            | 59 |

| <b>Figure 3. 7</b> Threshold voltage versus silicon thickness                                              | 60 |

| <b>Figure 3. 8</b> The proposed parameter extraction flow.                                                 | 61 |

| <b>Figure 3. 9</b> $I_{ds}$ versus $V_{gs}$ at low $V_{ds}$ for the device (L=50 nm, $t_{si}$ =5nm)        | 64 |

| <b>Figure 3. 10</b> $I_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=50 nm, $t_{si}$ =5nm) |    |

| <b>Figure 3. 11</b> Threshold voltage versus length at low $V_{ds}$ for $t_{si}$ =5nm.                     |    |

| <b>Figure 3. 12</b> Threshold voltage versus length at high $V_{ds}$ for $t_{si} = 5$ nm                   |    |

| Figure 3. 13 Threshold voltage versus silicon thickness                                                    |    |

| Figure 3. 14 Threshold voltage versus silicon thickness                                                      | . 69 |

|--------------------------------------------------------------------------------------------------------------|------|

| Figure 3. 15 Threshold voltage versus silicon thickness                                                      | . 70 |

| Figure 3. 16 Threshold voltage versus silicon thickness                                                      | . 71 |

| <b>Figure 3. 17</b> Threshold voltage versus length at low $V_{ds}$ for $t_{si} = 1.5$ nm.                   | . 72 |

| <b>Figure 3. 18</b> Threshold voltage versus length at high $V_{ds}$ for $t_{si}$ =1.5 nm.                   | . 72 |

| <b>Figure 3. 19</b> $I_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=15 nm, $t_{si}$ =1.5nm) | . 73 |

| Figure 3. 20 $I_{ds}$ versus $V_{gs}$ at different $V_{ds}$ for the device (L=15 nm, $t_{si}$ =1.5nm)        | . 74 |

| <b>Figure 3. 21</b> $I_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=30 nm, $t_{si}$ =3nm)   | . 75 |

| <b>Figure 3. 22</b> $I_{ds}$ versus $V_{gs}$ at different $V_{ds}$ for the device (L=30 nm, $t_{si}$ =3nm)   | . 76 |

| Figure 3. 23 $G_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=50 nm, $t_{si}$ =5nm)          | . 77 |

| Figure 3. 24 $G_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=15 nm, $t_{si}$ =1.5nm)        | . 78 |

| <b>Figure 3. 25</b> G m versus $V_{gs}$ at different $V_{ds}$ for the device (L=50 nm, $t_{si}$ =5nm)        | . 78 |

| Figure 3. 26 $G_m$ versus $V_{gs}$ at different $V_{ds}$ for the device (L=15 nm, $t_{si}$ =1.5nm)           | . 79 |

| <b>Figure 3. 27</b> $I_{ds}$ versus $V_{ds}$ at different $V_{gs}$ for the device (L=50 nm, $t_{si}$ =5nm)   | . 80 |

| <b>Figure 3. 28</b> Threshold voltage versus length at low $V_{ds}$ for $t_{si} = 5$ nm                      | . 81 |

| <b>Figure 3. 29</b> Threshold voltage versus length at high $V_{ds}$ for $t_{si}$ =5nm.                      | . 81 |

| <b>Figure 3. 30</b> Threshold voltage versus silicon thickness at high V <sub>ds</sub> for L=50nm            | . 82 |

# **List of Tables**

| Table 3. 1 | The list of the global parameters with its default and extracted values | 58 |

|------------|-------------------------------------------------------------------------|----|

| Table 3. 2 | The values of the local parameters for different devices                | 76 |

# **List of Symbols**

A\* Suggested model parameter

α Interaction factor representing the charge coupling between

the two gates

$\alpha_1$  Suggested model parameter  $\alpha_2$  Suggested model parameter

beta User specified quantity for Nanomos device simulator

β Constant of x direction

$\beta_d$   $\beta$  at the drain  $\beta_s$   $\beta$  at the source

C<sub>ox</sub> Oxide capacitance per unit area

$C_{ox}$  The oxide capacitance

$\begin{array}{ll} D_1 & Suggested \ model \ parameter \\ D_2 & Suggested \ model \ parameter \\ \Delta V_{th} & Threshold \ voltage \ shift \end{array}$

$\Delta \phi_i$  The work function difference

E Electric field

E<sub>s</sub> Surface electric field

$E_{c0}$  The original conduction band minimum of bulk silicon

$E_{\prime\prime}$  The electric field in the transport direction

El Electrostatic Integrity (EI) factor

$\epsilon_{si}$  Permittivity of silicon  $\epsilon_{ox}$  Oxide permittivity

f Dimensionless correction factor for Hu's model

*ħ* The reduced Planck constant

$\begin{array}{lll} k & Boltzman's \ constant \\ L_{el} & Electrical \ channel \ length \\ L & The \ effective \ channel \ length \\ \ell & The \ characteristic \ length \\ \lambda t_{box} & Depth \ in \ the \ buried \ oxide \\ \end{array}$

mu low User specified quantity for Nanomos device simulator

m\* The electron effective mass

μ Effective mobility

$\mu_o$  Model parameter which presents the value low field mobility  $n_o$  Mobile electrons concentration at the center of silicon film

n Mobile electrons concentration

n<sub>i</sub> Intrinsic carrier density

$N_{D}^{+}$  Ionized donors concentration  $N_{A}^{-}$  Ionized acceptors concentration

Ψ Electrostatic potential

$\psi_0$  Potential at the center of the silicon film

$\psi_{SL}$  The surface potential at the drain  $\psi_{S0}$  The surface potential at the source

$\psi_{oL}$  The potential at the center of the silicon film at the drain  $\psi_{o0}$  The potential at the center of the silicon film at the source

$\psi_s$  The surface potential

p Mobile holes concentration

$\rho(x)$  Charge density

$P_{I0}$  The zero-order term of the parameter  $P_{II}$  The length dependence parameter

P<sub>IT</sub> The silicon thickness dependence parameter

q<sub>in</sub> Normalized inversion charge

$\mathbf{q}_{\mathrm{s}}$  Normalized source inversion charge  $\mathbf{q}_{\mathrm{d}}$  Normalized drain inversion charge

q Electron charge

Q<sub>in</sub> Inversion charge

r Smoothing parameter

SC<sub>1</sub> Suggested model parameter

$\sigma_1$  Dimensionless factor which considers the drain induced

barrier lowering

$\sigma_2$  Dimensionless factor which considers the short channel

length

T Temperature  $t_{ox}$  Oxide thickness

t<sub>den</sub> Penetration depth of the gate field in the channel region

t<sub>si</sub> Silicon film thickness

vel sat User specified quantity for Nanomos device simulator

V<sub>ds</sub> Drain-to-source voltage

V<sub>bi</sub> Source or drain built-in potentialV Electron quasi-Fermi potential

$V_{\rm g}$  Gate voltage  $V_{\rm s}$  Source voltage  $V_{\rm d}$  Drain voltage

$V_{gs}$  Gate-to-source voltage

V<sub>fb</sub> Flat-band voltage

$V_{GF}$  The difference between the gate-to-source voltage and the

flat-band voltage

v<sub>sat</sub> A model parameter which presents the value of velocity

saturation

v<sub>deff</sub> the effective drain voltage

w Channel width

W<sub>0</sub>() The usual short-hand notation used for the principal branch

of the "Lambert-W" function

$x_j$  Junction depth

$\mathbf{X}_{\text{dep}}$  The depletion width in the substrate

## Introduction

Multi-gate MOSFET is one of the most promising semiconductor devices that was proven to be the best choice for future ICs, so, it has become an intensive subject of scientific research.

This thesis aims to study the different multi-gate structures and the recent compact models of the double gate structure. In this work, a new compact model for the undoped symmetric double gate is introduced. This model includes the most important short channel effects and the quantum confinement effect. Furthermore, an extraction flow for the model parameters is suggested.

The thesis consists of three chapters, list of contents, figures as well as a list of references.

#### Chapter 1

In this chapter, an overview of the bulk MOSFET scaling challenges and the different multi-gate structures are presented. Moreover, the behavior of the multi-gate structures against the short channel effects is explained. In addition, the major advantages of the double-gate MOSFET over the bulk MOSFET are explained. Finally, the most important quantum mechanical effects encountered in double-gate MOSFETs are illustrated

#### Chapter 2

In this chapter, the compact modeling concept is reviewed. Moreover, the most famous symmetric double-gate compact models (Taur, Ortiz, Hu and Common Symmetric Multi-Gate models) are presented stressing the advantages and disadvantages of each model. Finally, a brief overview on the device simulation and its advantages is given.

#### Chapter 3

In this chapter a new model based on Hu's model is proposed. Our new model is based on modifying the energy states quantization effect without the need to solve Schrödinger's equation. In addition, we present how to include the velocity saturation, channel length and drain induced barrier lowering effects. These effects represent the most important short channel effects. Furthermore, we show an extraction flow to extract our proposed model parameters. We use the Nanomos device simulator results as a reference to apply our extraction flow. Finally, we validate the model continuity and compare its results with Hu's model.

Finally, the thesis ends by extracting conclusions and stating future work that might be done based on this work.

Chapter 1 Literature Review

### CHAPTER 1

### **Literature Review**

### 1.1 Introduction

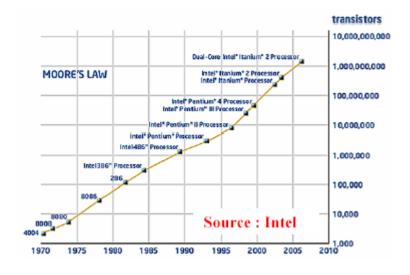

Silicon-based microelectronic devices have revolutionized our world in the past five decades. The need for higher computing power at cheaper cost has fueled incessant the CMOS scaling. It all started with the invention of integrated circuits in late 1950's that revealed the possibility of using transistors in almost all kinds of electronic circuits. The next major breakthrough came with the demonstration of the first metal-oxide semiconductor field-effect transistor (MOSFET) in 1960 by Kahng and Atalla which would enable cost-effective integration of large number of transistors with interconnections on a single silicon chip. Five years later, Gordon Moore published his famous paper describing the evolution of transistor density in integrated circuits. He predicted that the number of transistors per chip would quadruple every three years [1]. This prediction became well known as Moore's law and has been remarkably followed by semiconductor industry for the last forty years. Fig. 1.1 shows the Moore's Law with regard to the number of transistors in Intel's microprocessors. A modern day microprocessor has about a billion transistors.

Figure 1. 1 Moore's Law in microprocessors.

Over the past three decades, by reducing transistor gate lengths with each new generation of manufacturing technology, steady improvements in circuit performance (speed) and cost per function have been achieved. However, continued transistor scaling will not be as straightforward in the future as it has been in the past because fundamental materials and process limits are rapidly being approached. For all practical purposes, it