## NOISE ANALYSIS FOR LOW NOISE AMPLIFIER

## By

## Mai Mostafa Goda Ghareeb

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

or scien

Electronics and Communications Engineering

## NOISE ANALYSIS FOR LOW NOISE AMPLIFIER

## By

## Mai Mostafa Goda Ghareeb

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

**Electronics and Communications Engineering**

Under the Supervision of

| Prof. Dr. Ahmed M. Soliman               | Dr. Mohammed K. Ali Salama               |

|------------------------------------------|------------------------------------------|

|                                          |                                          |

| Professor of Electronics                 | Doctor                                   |

| Electronics and Communication departmen  | Electronics and Communication department |

| Faculty of Engineering, Cairo University | Faculty of Engineering, MSA University   |

## NOISE ANALYSIS FOR LOW NOISE AMPLIFIER

## By

## Mai Mostafa Goda Ghareeb

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

**Electronics and Communications Engineering**

| Approved by the Examining Committee                                    |                              |

|------------------------------------------------------------------------|------------------------------|

| Prof. Dr. Ahmed Mohamed Soliman ,                                      | Thesis Main Advisor          |

| Prof. Dr. Mohamed Riad El ghonemy,                                     | Internal Examiner            |

| Dr. Ahmed Hassan Kamel Madian,  - Director of post grade program, Nile | External Examiner University |

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2017 Engineer's Name: Mai Mostafa Goda Ghareeb

**Date of Birth:** 20 / 7 / 1989 **Nationality:** Egyptian

E-mail: mamn4444@gmail.com

**Phone:** 01062589178

**Address:** 24 Abd El-rahman Kassem St., El-Nozha,

Cairo, Egypt

**Registration Date:** 1/10/2012 **Awarding Date:** / / 2017 **Degree:** Master of Science

**Department:** Electronics and Communications Engineering

**Supervisors:**

Prof. Dr. Ahmed Mohamed Soliman Dr. Mohammed Khalaf Ali Salama

-Doctor, Faculty of Engineering, MSA University

**Examiners:**

Prof. Dr. Ahmed Mohamed Soliman (Thesis main advisor)

Prof. Mohamed Riad El ghonemy (Internal examiner)

Dr. Ahmed Hassan Kamel Madian (External examiner)

-Director of post grade program, Nile University

#### **Title of Thesis:**

Noise analysis for low noise amplifier

### **Key Words:**

Low noise amplifier; Global system for mobile communication; Global positioning system; Wireless local area network; Radio Frequency.

#### **Summary:**

The Low Noise Amplifier (LNA) is the first block in the receiver chain and is used to amplify the weak Radio Frequency (RF) signal arriving from external antenna, duplexer switch, and band select filter. To minimize the various noise contributions of the amplifier circuits, the noise source needs to be carefully analyzed and subsequently optimized. As wireless products such as cellular phones, Global System for Mobile communications (GSM), Global Positioning Satellite (GPS), Wireless Local Area Network (WLAN) ...etc become an everyday part of people's lives. The need for high performance at low cost and low power consumption becomes even more important in addition to the size of the wireless device.

The objective of the thesis is to enhance the performance of Salama and Soliman <u>Low Voltage Low Power (LVLP) CMOS RF LNA circuit using 90 nm Complementary Metal Oxide Semiconductor (CMOS) technology.</u>

And studying the wideband Balun-LNA with different topologies for different application then propose a new design to boost the gain with a moderate  $\underline{N}$  oise  $\underline{F}$  igure (NF) to cover a wideband frequency range from 3 GHz to 10 GHz.

# Acknowledgements

I wouldn't be able to express my sincerest thanks and gratitude and all respects to my great professors: Prof. Dr. Ahmed Mohamed Soliman and Dr. Mohammed Khalaf Ali Salama for all their help, support and encouragement.

This thesis would have never come to be without their continuous guidance, discussion and highly constructive comments.

Special thanks to my father, my mother and my little sister for their love, support and patience.

And I will always be grateful to my best friends.

# **Table of Contents**

| Acknowled    | gements                                                              | I     |

|--------------|----------------------------------------------------------------------|-------|

| Table of Co  | ontents                                                              | II    |

| List of Tab  | les                                                                  | V     |

| List of Figu | ıre                                                                  | VI    |

| Nomenclati   | ıre                                                                  | . VII |

| Abstract     |                                                                      | VIII  |

| Chapter 1    | : Introduction                                                       | 1     |

| 1.1 RF       | design is challenging                                                | 1     |

| 1.2 Re       | ceivers Architectures                                                | 3     |

| 1.3 Sig      | gnal propagation                                                     | 3     |

| 1.3.1        | Impedance matching                                                   | 3     |

| 1.3.2        | Scattering Parameters                                                | 4     |

| 1.E CN       | MOS LNA Circuit                                                      | 5     |

| 1.4.1        | CS versus CG configuration                                           | 5     |

| 1.1.7        | Cascode LNA                                                          | 9     |

| 1.8.7        | Single stage versus multi stage                                      | 9     |

| 1.5 Dit      | fferent techniques for input matching network to optimize NF of LVLP |       |

| CMOS R       | F LNA                                                                | 10    |

| 1.5.1        | Source inductive degeneration (SID)                                  | 11    |

| 1.5.2        | A Parallel LC (PLC) network                                          | 11    |

| 1.5.3        | A Series L (SL)                                                      | 12    |

| 1.5.4        | A parallel L (PL)                                                    | 13    |

| 1.6 Th       | esis objective                                                       | 14    |

| 1.7     | Org         | ganization of the Thesis                                        | 14   |

|---------|-------------|-----------------------------------------------------------------|------|

| Chapte  | er 2        | : Noise analysis for LVLP CMOS RF LNA                           | 15   |

| 2.1     | Int         | oduction                                                        | 15   |

| 2.2     | Sha         | neffer and Lee LNA                                              | 15   |

| 2.3     | Xia         | nomin Yang, Thomas X. Wu, and John McMacken LNA                 | 17   |

| 2.4     | The         | e modified 1V, 1.5GHz of Salama and Soliman LVLP CMOS RF LNA    |      |

| circu   | it          |                                                                 | 20   |

| 2.4     | <b>l</b> .1 | Gain analysis                                                   | 22   |

| 2.4     | 1.2         | Noise performance simulation result                             | 30   |

| 2.4     | 1.3         | S-parameters simulation result                                  | 31   |

| Chapte  | er 3        | : Wideband Balun-LNA with capacitive cross coupling and a casco | ding |

| gain bo | ostii       | ng technique                                                    | 33   |

| 3.1     | Int         | oduction                                                        | 33   |

| 3.1     | .1          | Background and Motivation                                       | 33   |

| 3.1     | .2          | IEEE 802.11 Wireless LNA                                        | 34   |

| 3.2     | The         | e conventional Balun-LNA                                        | 35   |

| 3.2     | 2.1         | Gain balancing                                                  | 37   |

| 3.2     | 2.2         | Noise canceling                                                 | 38   |

| 3.3     | AV          | Wideband improved Balun-LNA with Local Feedback                 | 41   |

| 3.4     | A 3         | 3-10 GHz Wideband Balun-LNA for LVLP applications in 90 nm CMOS |      |

| techn   | olog        | y                                                               | 43   |

| 3.4     | l.1         | Introduction                                                    | 43   |

| 3.4     | 1.2         | The proposed Circuit Design                                     | 43   |

| 3.5     | Co          | mparison between the proposed Balun-LNA with previous designs   | 50   |

| Chapte  | er 4        | : Conclusions and future work                                   | 52   |

| 4.1     | Co          | nclusion                                                        | 52   |

|     | 4.1.1     | The modified 1V, 1.5 GHz of Salama and Soliman LVLP CMOS RF LN.     | A  |

|-----|-----------|---------------------------------------------------------------------|----|

|     | circuit   |                                                                     | 52 |

|     | 4.1.2     | Wideband Balun-LNA with a capacitive cross coupling and a cascoding |    |

|     | gain boo  | osting techniques                                                   | 52 |

| 4   | .2 Fut    | ure work                                                            | 52 |

| RE  | FRENCI    | ES                                                                  | 53 |

| Apj | pendix A  | : Shaeffer Low Noise Amplifier [3]                                  | 59 |

| Apj | pendix B  | : The modified 1V, 1.5GHz of Salama and Soliman LVLP CMOS RF        |    |

| LN  | A circuit | [5]                                                                 | 61 |

| Apj | pendix C  | : A 3-10 GHz Wideband Balun-LNA for LVLP applications in 90 nm      |    |

| CM  | IOS tech  | nology                                                              | 69 |

# List of Tables

| Table 2-1: Comparison of LNA performances.                                 | 32 |

|----------------------------------------------------------------------------|----|

| Table 3-1: Comparison between the proposed Balun-LNA with previous designs | 51 |

# List of Figure

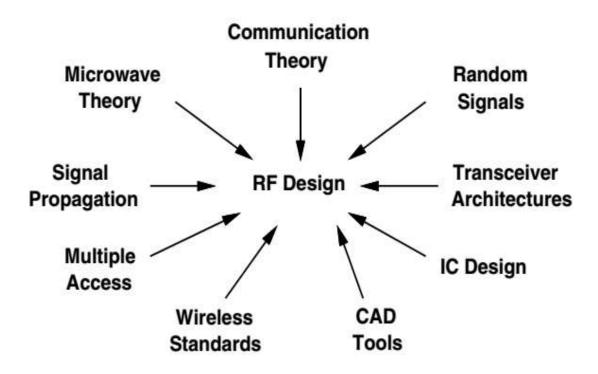

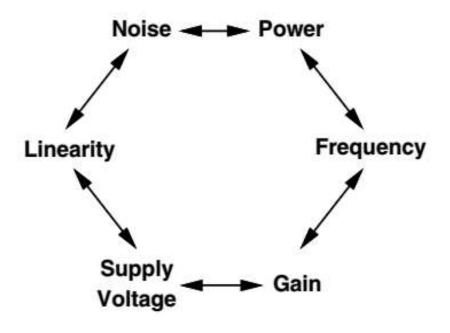

| Figure 1-1: Various disciplines necessary in RF design [1].                      | 2        |

|----------------------------------------------------------------------------------|----------|

| Figure 1-2: RF design hexagon [1].                                               | 2        |

| Figure 1-3: Common Source LNA input stage (CSLNA) [8]                            | 6        |

| Figure 1-4: Common Gate LNA input stage (CGLNA) [8].                             | 7        |

| Figure 1-5: Source inductive degeneration (SID) [24].                            | 11       |

| Figure 1-6: Parallel LC (PLC) network [24]                                       | 12       |

| Figure 1-7: A Series L (SL) [24]                                                 | 12       |

| Figure 1-8: A parallel L (PL) [24].                                              | 13       |

| Figure 2-1: Shaeffer and Lee CMOS LNA [3].                                       | 17       |

| Figure 2-2: Yang, Wu, and McMacken LNA schematic [29].                           | 19       |

| Figure 2-3: The modified 1V, 1.5 GHz of Salama and Soliman LVLP CMOS R           | F LNA    |

| [5]                                                                              | 21       |

| Figure 2-4: Small signal equivalent model for the proposed design                | 22       |

| Figure 2-5 : Euivalent model of mutual inductance                                | 23       |

| Figure 2-6: Gain from Matlab calculations.                                       | 30       |

| Figure 2-7: Noise Figure of the proposed design.                                 | 30       |

| Figure 2-8: S-parameter of the proposed design.                                  | 31       |

| Figure 3-1: The basic common-gate common-source topology in which the nois       | e of the |

| CG-transistor can be canceled [43].                                              | 36       |

| Figure 3-2: (a) Noise figure, (b) voltage gain and (c) gain imbalance versus imp | edance   |

| scaling factor 'n ' for three different cases [43]                               | 40       |

| Figure 3-3: CG-CS LNA with local feedback [44]                                   | 42       |

| Figure 3-4: The proposed Balun-LNA.                                              | 44       |

| Figure 3-5: Small signal model of cascoded CS stage.                             | 45       |

| Figure 3-6: Gain of the proposed design                                          | 49       |

| Figure 3-7: Input return loss of the propsed design.                             | 49       |

| Figure 3-8: NF of the proposed design.                                           | 50       |

### **Nomenclature**

#### **Abbreviations:**

ADS Advanced Design System

Balun Balanced-Unbalanced

CG Common-Gate

CS Common-Source

CMOS Complementary Metal Oxide Semiconductor

dB Decibel

DC Direct Current

FCC Federal Communication Commission

GSM Global System for Mobile Communication

GPS Global Positioning Satellite

IC Integrated Circuit

ISM Instrumentation, Scientific and Medical

LNA Low Noise Amplifier

LO Local Oscillator

LVLP Low Voltage Low Power

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NF Noise Figure

OFDM Orthogonal Frequency Division Multiplexing

Q Quality Factor

RF Radio Frequency

SNR Signal to Noise Ratio

SID Source Inductive Degeneration

UWB Ultra Wide Band

UNII Unlicensed National Information Infrastructure

WLAN Wireless Local Area Network

WPAN Wireless personal Area Network

WMTS Wireless Medical Telemetry Service

### **Abstract**

The Low Noise Amplifier (LNA) is the first block in the receiver chain and is used to amplify the weak Radio Frequency (RF) signal arriving from external antenna, duplexer switch, and band select filter. The main goals of designing LNA circuit are minimizing the NF, providing sufficient gain and linearity and providing a  $50\Omega$  input impedance to terminate the transmission line delivers signal from the antenna to the amplifier.

To minimize the various noise contributions of the amplifier circuits, the noise source needs to be carefully analyzed and subsequently optimized. As wireless products such as cellular phones, <u>Global System for Mobile communications (GSM)</u>, <u>Global Positioning Satellite (GPS)</u>, <u>Wireless Local Area Network (WLAN)</u> ...etc become an everyday part of people's lives. The need for higher performance at low cost and low power consumption becomes even more important in addition to the size of the wireless device [1].

As the first active stage of receivers, LNAs play a critical role in the overall performance and their design is governed by a trade-off among the following parameters.

- 1) Power Dissipation

- 2) Noise Figure

- 3) Linearity

- 4) Gain

- 5) Bandwidth

- 6) Input Matching (antenna-LNA matching)

Doing the analysis for the proposed circuits and calculate the gain, the input referred noise and the Noise Figure (NF) trying to minimize the NF as much as possible to achieve higher performance for the overall design then studying the S-parameter for each design to know the incident, reflected power and the power loss in order to achieve good matching and enhance it by adding an inductor. The objective of the thesis is to get better performance of Salama and Soliman Low Voltage Low Power (LVLP) CMOS RF LNA circuit using 90 nm CMOS technology. Studying different designs of a wideband Balun-LNA for many applications then achieve a new design to boost the gain with a moderate NF for a wideband frequency range from 3 GHz to 10 GHz.

## **Chapter 1**: Introduction

The high-speed wireless communication systems development puts growing request on integrated low-cost RF devices with multi-GHz bandwidth which operate at the lowest power consumption and supply voltage. The main block in designing broadband receivers for multiband wireless communication standards is the wideband LNA [2]. Still the challenge in designing CMOS RF front end circuit is to provide high performance, low cost, low power consumption [3], [4]. Today the present goal is to reduce the power consumption, which leads to an increase in the battery-use time and in cost as well [5].

## 1.1 RF design is challenging

In spite of many decades of work on RF and microwave theory and two decades of research on RF <u>Integrated Circuits</u> (ICs), the design and implementation of RF circuits and transceivers remain challenging. Because of three reasons:

First, as shown in Figure 1-1, RF design depends on a multitude of disciplines, which requires a good understanding of fields that are seemingly irrelevant to integrated circuits. Most of these fields have been under studying for more than half a century, presenting a massive body of knowledge to a person entering RF IC design.

Second, the persistent need for higher performance, lower cost and greater functionality continues to present new challenges. The early RF IC design work in the 1990s struggled to integrate one transceiver, perhaps along with the digital baseband processor, on a single chip.

Third, RF circuits and transceivers must deal with plentiful trade-offs, summarized in the "RF design hexagon" of Figure 1-2. For example, consuming a greater power or scarifying linearity is a must to lower the noise of a front-end amplifier.

Figure 1-1: Various disciplines necessary in RF design [1].

Figure 1-2: RF design hexagon [1].

### 1.2 Receivers Architectures

A transmitter, a receiver and a communication channel, in which the transmitted signals propagate, are the main blocks of a communication system. In the case of wireless systems, the information sent by the transmitter is involved in a RF signal via a modulation process, i.e. by varying at least one of the signal's characteristics (amplitude, frequency or phase). Once signal arrives at the receiver, the information needs to be recovered from the original RF signal through a demodulation process. The communication medium, mainly air (in the case of wireless communications), is not ideal since the signals received are usually very weak (~ microvolts) and are liable to suffer interference from other, possibly stronger, signals. So it is important to be capable of eliminating unwanted signals and isolating the signal of interest, so that it can be subsequently amplified and converted to baseband to go through demodulation, permitting the information contained in the signal to be recovered.

To carry more information in a signal, the signals are converted to high frequency for transmission and then converted back for the baseband for reception. The size of the antenna is also depends on the frequency of the transmitted signal. As the size is typically proportional to the wavelength of the signal, the required antennas are smaller. Unfortunately, the effect of parasitics (impedances, capacitors, etc.) is higher at high frequencies.

# 1.3 Signal propagation

## 1.3.1 Impedance matching

Impedance Matching was originally developed for electrical power, but can be applied to any other field where a form of energy (not necessarily electrical) is transferred between a source and a load. The first impedance matching concept in RF domain was related to antenna matching. Designing an antenna can be seen as matching the free space to a transmitter or a receiver.

The main objective of impedance matching is to match two different terminations  $(R_{source} \text{ and } R_{load})$  through a specific pass-band, without having control over stop-band frequencies. We may assume that component losses are negligible but parasitic effects need to be considered. The main role in any impedance matching scheme is to force a load impedance to be similar to the complex conjugate of the source impedance, and maximum power can be transferred to the load.